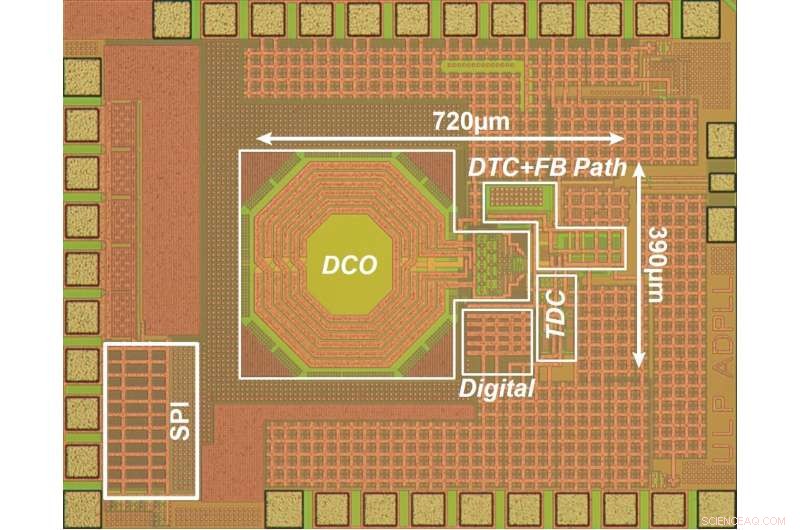

Il DPLL a N frazionario proposto occupa un'area di 0,25 mm 2 in CMOS a 65 nanometri. Credito:Kenichi Okada

Gli scienziati del Tokyo Institute of Technology hanno sviluppato un avanzato sintetizzatore di frequenza ad anello ad aggancio di fase (PLL) che può ridurre drasticamente il consumo di energia. Questo PLL digitale potrebbe essere un interessante elemento costitutivo per Bluetooth Low Energy (BLE) e altre tecnologie wireless per supportare un'ampia gamma di applicazioni Internet of Things (IoT).

Come elemento fondamentale dei sistemi di comunicazione wireless, i sintetizzatori di frequenza devono soddisfare requisiti esigenti. Sebbene i sintetizzatori di frequenza PLL analogici siano stati lo standard per molti anni, gli ingegneri del settore IoT stanno rivolgendo sempre più la loro attenzione ai cosiddetti PLL digitali (DPLL) per ottenere un funzionamento a bassissima potenza.

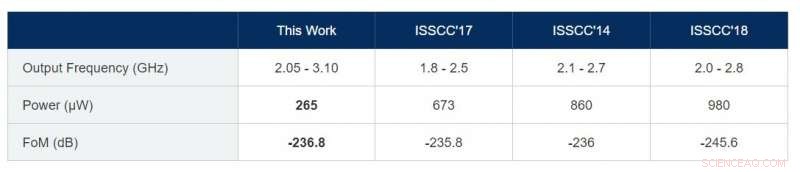

Kenichi Okada, professore associato presso il Dipartimento di ingegneria elettrica ed elettronica del Tokyo Institute of Technology e il suo gruppo ora segnalano un DPLL a N frazionario che raggiunge un consumo energetico di soli 265 microwatt (μW), una cifra che è meno della metà del consumo energetico più basso raggiunto fino ad oggi (980 μW). (Tabella 1)

I ricercatori hanno scoperto che il consumo energetico complessivo potrebbe essere notevolmente ridotto utilizzando un sistema di controllo automatico del feedback. "Questo percorso di feedback a commutazione automatica consuma una potenza di 68 μW, che porta ad un consumo energetico di 265 μW per l'intero DPLL, "dice Okada.

Il promettente DPLL potrebbe essere utilizzato come componente per processori, memorie e una vasta nuova gamma di dispositivi IoT che dovrebbero essere sia economici che ecologici grazie al funzionamento a bassissima potenza. Okada osserva che i primi esperimenti mostrano che il DPLL potrebbe prolungare la durata della batteria di quattro volte.

Gli scienziati del Tokyo Institute of Technology hanno sviluppato un avanzato sintetizzatore di frequenza ad anello ad aggancio di fase (PLL) che può ridurre drasticamente il consumo di energia. Questo PLL digitale potrebbe essere un interessante elemento costitutivo per Bluetooth Low Energy (BLE) e altre tecnologie wireless per supportare un'ampia gamma di applicazioni Internet of Things (IoT). Credito:Kenichi Okada

Questo documento si basa in parte sui risultati ottenuti da un progetto commissionato dalla New Energy and Industrial Technology Development Organization (NEDO).

Questo lavoro è stato presentato nella sessione sui sintetizzatori di frequenza alla Conferenza internazionale sui circuiti a stato solido 2019 (ISSCC), il forum annuale più importante al mondo sui circuiti a stato solido e sui sistemi su chip.