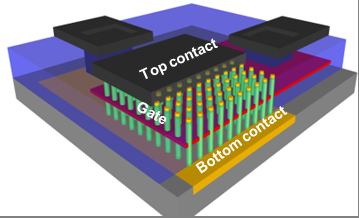

Schema di un nano-transistor 3D che mostra il cancello (rosso) che circonda i nanofili verticali (verde) e che separa i contatti alle estremità di ciascun nanofilo (beige). Credito:© X-L Han e G. Larrieu

Una nuova svolta potrebbe spingere i limiti della miniaturizzazione dei componenti elettronici più in là di quanto si ritenesse possibile. Un team del Laboratoire d'Analyse et d'Architecture des Systèmes (LAAS) e dell'Institut d'Électronique, de Microélectronique et de Nanotechnologie (IEMN) ha costruito un transistor nanometrico che mostra proprietà eccezionali per un dispositivo delle sue dimensioni. Per ottenere questo risultato, i ricercatori hanno sviluppato una nuova architettura tridimensionale costituita da un array verticale di nanofili la cui conduttività è controllata da un cancello che misura solo 14 nm di lunghezza.

Pubblicato in Nanoscala , questi risultati aprono la strada verso alternative alle strutture planari utilizzate nei microprocessori e nelle unità di memoria. L'uso di transistor 3D potrebbe aumentare significativamente la potenza dei dispositivi microelettronici.

I "mattoni" della microelettronica, i transistor sono costituiti da un componente semiconduttore, chiamato canale, collegamento di due terminali. Il flusso di corrente tra questi terminali è controllato da un terzo terminale, chiamato cancello. Agendo come un interruttore, il gate determina se il transistor è acceso o spento. Negli ultimi 50 anni, i transistor sono stati costantemente ridotti di dimensioni, consentendo lo sviluppo di dispositivi microelettronici sempre più potenti. Però, è generalmente accettato che i transistor di oggi, con la loro architettura planare, si stanno avvicinando ai limiti della miniaturizzazione:esiste una dimensione minima al di sotto della quale il controllo del gate sul canale diventa sempre meno efficace. In particolare, le correnti di dispersione iniziano a interferire con le operazioni logiche eseguite dall'array di transistor. Per superare questo problema, ricercatori di tutto il mondo stanno studiando alternative che consentiranno di continuare la corsa alla miniaturizzazione.

Un team di ricercatori del LAAS e dell'IEMN ha ora costruito il primo transistor nanometrico veramente tridimensionale. Il dispositivo è costituito da una stretta matrice verticale di nanofili di circa 200 nm di lunghezza che collega due superfici conduttive. Un cancello di cromo circonda completamente ogni nanofilo e controlla il flusso di corrente, con conseguente controllo ottimale del transistor per un sistema di queste dimensioni. La porta è lunga solo 14 nm, rispetto ai 28 nm dei transistor dei chip odierni, ma la sua capacità di controllare la corrente nel canale del transistor soddisfa i requisiti della microelettronica contemporanea.

Questa architettura potrebbe portare allo sviluppo di microprocessori in cui i transistor sono impilati insieme. Il numero di transistor in un dato spazio potrebbe così essere notevolmente aumentato, insieme alla capacità prestazionale di microprocessori e unità di memoria. Un altro vantaggio significativo di questi componenti è che sono relativamente semplici da fabbricare e non richiedono litografia ad alta risoluzione. Inoltre, questi transistor 3D potrebbero essere facilmente integrati nei dispositivi microelettronici convenzionali utilizzati oggi dall'industria.

È stato depositato un brevetto per questi transistor. I ricercatori ora intendono continuare i loro sforzi per ridurre ulteriormente le dimensioni del cancello, che ritengono potrebbe essere inferiore a 10 nm pur fornendo un controllo soddisfacente sul transistor. Inoltre, il team è alla ricerca di partner industriali che aiutino a progettare i dispositivi elettronici del futuro utilizzando l'architettura 3D di questi nuovi transistor.