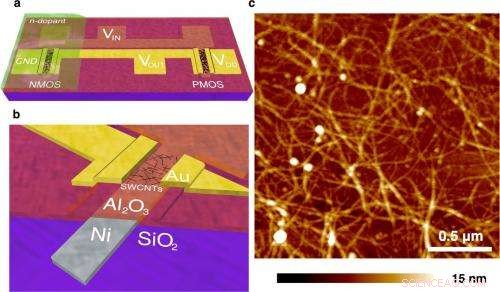

Illustrazioni di (a) l'invertitore CNT CMOS e (b) una sezione trasversale di un singolo transistor CNT, incluso un gate Ni di 25 nm di spessore che consente un consumo energetico estremamente basso. (c) Immagine al microscopio a forza atomica della morfologia del film di CNT nella regione del canale del transistor. Credito:Geier, et al. ©2013 American Chemical Society

(Phys.org) —I ricercatori hanno dimostrato un nuovo dispositivo logico basato su nanotubi di carbonio (CNT) che consuma solo 0,1 nanowatt (nW) nei suoi stati ON e OFF statici, che rappresenta il valore più basso riportato di 3 ordini di grandezza per i dispositivi logici CMOS basati su CNT. Il dispositivo potrebbe fungere da elemento costitutivo per grandi aree, circuiti logici CNT a bassissima potenza che possono essere utilizzati per realizzare una varietà di applicazioni di nanoelettronica.

I ricercatori, Michael L. Geier, et al., alla Northwestern University di Evanston, Illinois, e l'Università del Minnesota a Minneapolis, hanno pubblicato il loro articolo sulla logica CNT subnanowatt in un recente numero di Nano lettere .

"Un moderno circuito integrato ha più di 1 miliardo di transistor, " coautore Mark C. Hersam, Professore di Scienza e Ingegneria dei Materiali, Chimica, e Medicina alla Northwestern University, detto Phys.org . "Di conseguenza, la dissipazione di potenza per transistor deve essere molto bassa affinché l'intero circuito abbia un consumo energetico ragionevole. Infatti, è generalmente accettato che il consumo di energia è il fattore limitante chiave per ottenere ulteriori aumenti della complessità (cioè, numero di transistor) nei circuiti integrati."

Come spiegano i ricercatori, uno dei maggiori vantaggi dell'architettura CMOS è che ha un consumo energetico intrinsecamente basso. Questo vantaggio deriva dal fatto che, a differenza di altre architetture logiche, uno dei due tipi di transistor (tipo p o tipo n) viene spento a regime in ciascuna porta logica nei dispositivi CMOS.

Per sfruttare appieno questo potenziale di consumi estremamente bassi, i transistor di tipo p e di tipo n devono avere tensioni di soglia sintonizzate con precisione e ben separate, quali sono i livelli di tensione che determinano se il dispositivo è acceso o spento. Finora, questo problema delle tensioni di soglia non è stato affrontato, e i ricercatori qui l'hanno identificata come la sfida chiave che limita la realizzazione di un'elettronica CMOS basata su CNT altamente integrata.

Nel loro studio, i ricercatori hanno utilizzato una struttura a gate metallico per ottenere tensioni di soglia simmetriche e chiaramente separate per transistor CNT di tipo p e n, con conseguente consumo energetico estremamente basso. Negli stati statici, in cui il dispositivo è ON o OFF, il consumo di energia è inferiore a 0,1 nW. Nel punto medio dello stato di trasferimento, quando entrambi i transistor di tipo p e di tipo n sono simultaneamente nello stato ON, la tensione raggiunge il suo picco a 10 nW.

Collegando più transistor CNT in varie configurazioni, i ricercatori hanno dimostrato inverter, Porte logiche NAND e NOR. Nel futuro, queste porte possono essere integrate in circuiti complessi, dove possono fornire un consumo di energia statica subnanowatt insieme agli altri vantaggi dei CNT, come la processabilità e la flessibilità della soluzione.

"Ora stiamo lavorando per realizzare circuiti più complicati, dove avremo sostanzialmente più transistor e porte logiche in cascata, "Hersam ha detto. "Abbiamo anche interesse a combinare i nanotubi di carbonio con altri materiali nanoelettronici emergenti nel nostro laboratorio (ad es. bisolfuro di molibdeno [MoS 2 ])."

© 2013 Phys.org. Tutti i diritti riservati.