Lo stress meccanico di trazione può avere un effetto utile per alcuni transistor, dove il ceppo atomico risultante consente alle sue coppie elettrone-lacuna che trasportano corrente una migliore mobilità. Però, quando tale stress viene applicato all'intero dispositivo, come è un approccio popolare tramite l'uso dei cosiddetti contact etching stop layer (CESL), la regione di deriva adiacente al canale allungato viene compressa e si traduce in prestazioni ridotte.

Un team di ricerca in Cina ha sviluppato un nuovo metodo CESL che introduce sollecitazioni di trazione sia nel canale che nella regione di deriva, migliorare le prestazioni complessive offrendo una bassa resistenza alla deriva, alta frequenza di taglio e caratteristiche di rottura desiderabili. Il loro lavoro è descritto in un articolo apparso questa settimana sulla rivista I progressi dell'AIP .

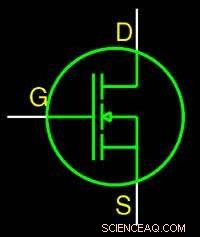

Il team di ricercatori si è interessato al metodo a causa del lavoro svolto sulle tecniche del silicio teso. Durante la ricerca sui transistor ad effetto di campo (MOSFET) a semiconduttore a metaossido teso, i ricercatori hanno visto che lo stress nella regione di source/drain era inverso rispetto allo stress della regione del canale. Sulla base di queste osservazioni, hanno iniziato a studiare come potrebbero utilizzare questo fenomeno in un modo che potrebbe migliorare le prestazioni.

Questa nuova ricerca si è concentrata sui dispositivi PSOI (Silicio su isolante parziale) che introducono sollecitazioni di trazione sia nel canale che nella regione di deriva utilizzando i CESL. I risultati della simulazione hanno anche mostrato che il dispositivo PSOI offre prestazioni in frequenza e capacità di guida migliori rispetto ai dispositivi non sforzati.

"La cosa più difficile per noi è stata trovare un prezzo basso, Metodo compatibile con CMOS per l'applicazione di sollecitazioni meccaniche, " ha detto Xiangzhan Wang, dell'Università di Scienze e Tecnologie Elettroniche della Cina. "Durante il processo di fabbricazione, il wafer si piega man mano che cresce lo stress film (Si3N4), il che crea un problema nel trattenere il wafer nelle apparecchiature di processo."

I risultati dell'esperimento, però, maggiore fiducia che la nuova tecnica di deformazione non potesse essere applicata solo a piccoli dispositivi, ma anche a dispositivi piuttosto grandi per ottenere un miglioramento delle prestazioni. Con i risultati, anche il team di ricerca è rimasto sorpreso dal livello di miglioramento fornito alle loro simulazioni.

"Nella nostra simulazione, l'LDMOSFET di tipo n PSOI sottoposto a tensione di trazione ha mostrato un miglioramento della corrente di guida del 20-30% rispetto al normale LDMOSFET Si, " ha detto Wang. "Ma quando abbiamo usato questo metodo di ceppo con un prodotto commerciale Si LDMOS, la corrente di pilotaggio è raddoppiata ottenendo un aumento della corrente di oltre il 100 percento, che è stato abbastanza sorprendente per noi."

Mentre questo lavoro ha contribuito alla comprensione dei meccanismi di Si tesi, c'è ancora molto da migliorare e capire.

"Le prossime direzioni di ricerca per il team sono ottimizzare il processo di fabbricazione di questi dispositivi al fine di ottenere una migliore stabilità e provare ad applicare lo stesso metodo a un dispositivo non simmetrico come un tunnel FET, "Ha detto Wang.