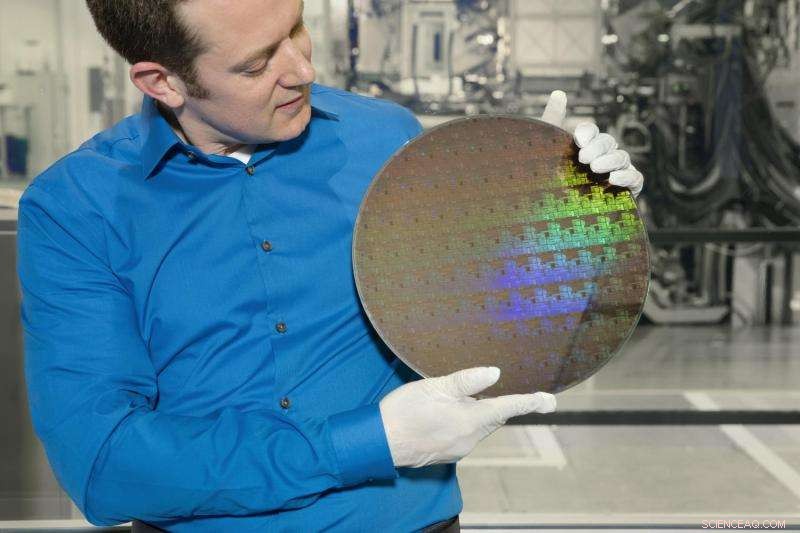

Lo scienziato di IBM Research Nicolas Loubet detiene un wafer di chip con transistor a nanofoglio di silicio da 5 nm prodotti utilizzando un processo innovativo in grado di fornire un miglioramento delle prestazioni del 40% a potenza fissa, o 75% di risparmio energetico a prestazioni equivalenti. Attestazione:Connie Zhou

IBM, i suoi partner della Research Alliance Globalfoundries e Samsung, e i fornitori di apparecchiature hanno sviluppato un processo per la prima volta nel settore per costruire transistor a nanofoglio di silicio che consentiranno di ottenere chip da 5 nanometri (nm). I dettagli del processo saranno presentati alla conferenza 2017 Symposia on VLSI Technology and Circuits a Kyoto, Giappone. In meno di due anni dallo sviluppo di un chip nodo di test a 7 nm con 20 miliardi di transistor, gli scienziati hanno aperto la strada a 30 miliardi di interruttori su un chip delle dimensioni di un'unghia.

Il conseguente aumento delle prestazioni aiuterà ad accelerare il calcolo cognitivo, l'Internet delle cose (IoT), e altre applicazioni ad alta intensità di dati fornite nel cloud. Il risparmio energetico potrebbe anche significare che le batterie degli smartphone e di altri prodotti mobili potrebbero durare da due a tre volte più a lungo dei dispositivi odierni, prima di dover essere addebitato.

Scienziati che lavorano come parte della Research Alliance guidata da IBM presso il SUNY Polytechnic Institute Colleges of Nanoscale Science and Engineering's NanoTech Complex ad Albany, NY ha raggiunto la svolta utilizzando pile di nanofogli di silicio come struttura del dispositivo del transistor, invece dell'architettura standard FinFET, che è il progetto per l'industria dei semiconduttori fino alla tecnologia dei nodi a 7 nm.

"Affinché le imprese e la società soddisfino le esigenze del cognitive e del cloud computing nei prossimi anni, il progresso nella tecnologia dei semiconduttori è essenziale, " disse Arvind Krishna, vicepresidente anziano, Cloud ibrido, e direttore, Ricerca IBM. "Ecco perché IBM persegue in modo aggressivo architetture e materiali nuovi e diversi che spingono i limiti di questo settore, e li porta sul mercato in tecnologie come i mainframe e i nostri sistemi cognitivi".

Scienziati IBM presso il SUNY Polytechnic Institute Colleges of Nanoscale Science and Engineering's NanoTech Complex ad Albany, NY prepara wafer di prova con transistor a nanofoglio di silicio da 5 nm, caricato nella capsula unificata ad apertura frontale, o FOUP, per testare un processo innovativo per la costruzione di transistor a 5 nm utilizzando nanofogli di silicio. Attestazione:Connie Zhou

La dimostrazione del transistor a nanofoglio di silicio, come dettagliato nel documento della Research Alliance Stacked Nanosheet Gate-All-Around Transistor per abilitare lo scaling oltre FinFET, e pubblicato da VLSI, dimostra che i chip a 5 nm sono possibili, più potente, e non troppo lontano nel futuro.

Rispetto alla tecnologia all'avanguardia a 10 nm disponibile sul mercato, una tecnologia a 5 nm basata su nanosheet può fornire un miglioramento delle prestazioni del 40% a potenza fissa, o 75% di risparmio energetico a prestazioni equivalenti. Questo miglioramento consente una spinta significativa per soddisfare le esigenze future dei sistemi di intelligenza artificiale (AI), realtà virtuale e dispositivi mobili.

Costruire un nuovo interruttore

"Questo annuncio è l'ultimo esempio della ricerca di livello mondiale che continua ad emergere dalla nostra innovativa partnership pubblico-privato a New York, "ha detto Gary Patton, CTO e Head of Worldwide R&D presso Globalfoundries. "Mentre avanziamo verso la commercializzazione di 7 nm nel 2018 presso il nostro impianto di produzione Fab 8, stiamo attivamente perseguendo tecnologie di prossima generazione a 5 nm e oltre per mantenere la leadership tecnologica e consentire ai nostri clienti di produrre un più piccolo, Più veloce, e una generazione di semiconduttori più efficiente in termini di costi."

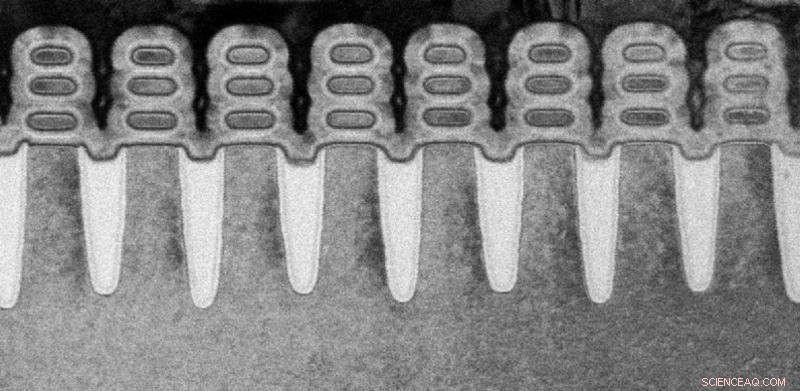

Nella foto:una scansione del transistor a 5 nm di IBM Research Alliance, costruito utilizzando un processo innovativo per impilare nanofogli di silicio come struttura del dispositivo, raggiungendo una scala di 30 miliardi di interruttori su un chip delle dimensioni di un'unghia che fornirà miglioramenti significativi in termini di potenza e prestazioni rispetto ai moderni chip a 10 nm. Credito:IBM

IBM Research ha esplorato la tecnologia dei semiconduttori a nanofogli per più di 10 anni. Questo lavoro è il primo nel settore a dimostrare la fattibilità di progettare e fabbricare dispositivi a nanofogli impilati con proprietà elettriche superiori all'architettura FinFET.

Questo stesso approccio di litografia Extreme Ultraviolet (EUV) utilizzato per produrre il nodo di test a 7 nm e i suoi 20 miliardi di transistor è stato applicato all'architettura del transistor a nanosheet. Usando la litografia EUV, la larghezza dei nanosheet può essere regolata continuamente, il tutto all'interno di un singolo processo di produzione o progettazione del chip. Questa regolazione consente la regolazione fine delle prestazioni e della potenza per circuiti specifici, cosa non possibile con l'odierna produzione di architetture a transistor FinFET, che è limitato dalla sua altezza della pinna che trasporta corrente. Perciò, mentre i chip FinFET possono scalare fino a 5 nm, la semplice riduzione dello spazio tra le alette non fornisce un flusso di corrente maggiore per prestazioni aggiuntive.

"L'annuncio di oggi continua il modello di collaborazione pubblico-privato con IBM che sta dando energia al SUNY-Polytechnic, di Albany, e la leadership e l'innovazione dello Stato di New York nello sviluppo di tecnologie di prossima generazione, " ha detto il dottor Bahgat Sammakia, Presidente ad interim, Istituto Politecnico SUNY. "Riteniamo che l'abilitazione del primo transistor a 5 nm sia una pietra miliare significativa per l'intero settore dei semiconduttori mentre continuiamo a spingerci oltre i limiti delle nostre attuali capacità. La partnership di SUNY Poly con IBM e Empire State Development è un perfetto esempio di come l'industria, Il governo e il mondo accademico possono collaborare con successo e avere un impatto ampio e positivo sulla società".

Parte dei 3 miliardi di dollari di IBM, investimento quinquennale in ricerca e sviluppo di chip (annunciato nel 2014), la prova della scalabilità dell'architettura a nanosheet fino a un nodo a 5 nm continua l'eredità di contributi storici di IBM all'innovazione del silicio e dei semiconduttori. Includono l'invenzione o la prima implementazione della DRAM a cella singola, le leggi di scaling di Dennard, fotoresist amplificati chimicamente, cablaggio di interconnessione di rame, Silicio su isolante, ingegneria tesa, microprocessori multi core, litografia ad immersione, SiGe ad alta velocità, dielettrici di gate ad alto k, DRAM incorporata, Impilamento di chip 3-D e isolatori Air gap.