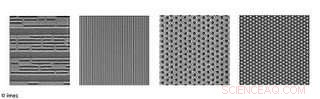

Modello singolo EUV (a sinistra) dello strato N5 32nm metallo-2, (al centro) linee dense passo 32nm, e (a destra) fori e pilastri di contatto esagonali da 40 nm. Credito:IMEC

Imeco, il polo mondiale di ricerca e innovazione nella nanoelettronica e nella tecnologia digitale, continua a far progredire la prontezza della litografia EUV con particolare attenzione all'esposizione singola EUV di strati metallici Logic N5, e di array di fori densi aggressivi. L'approccio di Imec per abilitare il patterning singolo EUV a queste dimensioni si basa sulla co-ottimizzazione di vari abilitatori di litografia, compresi i materiali, metrologia, regole di progettazione, post-elaborazione e una comprensione fondamentale dei processi EUV critici. I risultati, che sarà presentato in più articoli alla SPIE Advanced Lithography Conference 2018 di questa settimana, mirano a incidere in modo significativo sulla roadmap tecnologica e sui costi dei wafer dei nodi tecnologici a breve termine per la logica e la memoria.

Con l'industria che sta apportando miglioramenti significativi alla disponibilità dell'infrastruttura EUV, è previsto il primo inserimento della litografia EUV nella produzione ad alto volume nel metallo critico back-end-of-line e tramite strati del nodo tecnologico N7 Logic di fonderia, con passi metallici nell'intervallo 36-40 nm. La ricerca di Imec si concentra sul nodo successivo (passo 32nm e inferiore), dove vengono presi in considerazione vari approcci di patterning. Questi approcci variano notevolmente in termini di complessità, costo del wafer, e tempo per cedere, e includono variazioni del multipatterning EUV, EUV ibrido e multipatterning ad immersione, e EUV esposizione singola. L'anno scorso allo SPIE, imec ha presentato molti progressi nel multipatterning ibrido e ha rivelato varie sfide della soluzione a esposizione singola EUV più conveniente. Quest'anno, imec e i suoi partner mostrano notevoli progressi verso l'abilitazione di queste dimensioni con l'esposizione singola EUV.

Il percorso di Imec prevede una co-ottimizzazione di vari abilitatori litografici, compresi i materiali resistenti, stack e post-elaborazione, metrologia, litografia computazionale e co-ottimizzazione tecnologia-design, e una comprensione fondamentale dei meccanismi di reazione di resistenza dell'EUV e degli effetti stocastici. Sulla base di questo approccio globale, imec ha dimostrato progressi promettenti compresi i risultati elettrici iniziali, sulla singola esposizione EUV concentrandosi su due casi d'uso principali:logico N5 32nm pitch metal-2 layer e array di fori di contatto pitch 36nm.

Lavorando con i suoi numerosi partner di materiali, imec ha valutato diverse strategie di materiali resistivi, compresi resist chimicamente amplificati, resist contenenti metalli e resist a base di sensibilizzanti. Particolare attenzione è stata posta alla resistenza alla rugosità, e ai nanofallimenti come i nanoponti, linee spezzate o contatti mancanti indotti dal regime di patterning EUV stocastico. Questi errori stocastici stanno attualmente limitando le dimensioni minime per la singola esposizione EUV. Sulla base di questo lavoro, imec ha approfondito la comprensione fondamentale degli stocastici e ha identificato le dipendenze primarie che influenzano i fallimenti. Inoltre, sono state impiegate varie tecniche metrologiche e strategie ibride per garantire un quadro accurato della realtà degli stocastici. Imec riporterà su questo lavoro collettivo, dimostrando le prestazioni di vari line-space all'avanguardia e resistenze a foro di contatto.

Poiché i progressi dei materiali resistenti da soli probabilmente non saranno sufficienti per soddisfare i requisiti, imec si è concentrata anche sulla co-ottimizzazione della fotomaschera, pila di pellicole, Esposizioni EUV ed etch verso un flusso di patterning integrato per ottenere un patterning completo delle strutture. Ciò è stato fatto utilizzando tecniche di litografia computazionale come la correzione ottica di prossimità e l'ottimizzazione della maschera di origine, integrato dalla co-ottimizzazione della tecnologia di progettazione per ridurre le aree delle celle delle librerie standard. Finalmente, le tecniche di post-elaborazione basate sull'incisione volte a levigare le immagini dopo le fasi di litografia producono risultati incoraggianti per le caratteristiche dense. La co-ottimizzazione di queste manopole multiple è la chiave per ottenere un modello ottimizzato e un controllo degli errori di posizionamento dei bordi.

Greg McIntyre, Il direttore del patterning avanzato di imec riassume:

"Riteniamo che questi siano progressi molto promettenti per consentire a EUV di ottenere in modo affidabile un singolo modello a queste dimensioni aggressive. Ciò avrebbe un impatto significativo sull'efficacia dei costi delle soluzioni di modello per i prossimi nodi tecnologici".