I nanotubi di carbonio, grandi molecole cilindriche composte da atomi di carbonio ibridati disposti in una struttura esagonale, hanno recentemente attirato una notevole attenzione tra gli ingegneri elettronici. Grazie alla loro configurazione geometrica e alle proprietà elettroniche vantaggiose, queste molecole uniche potrebbero essere utilizzate per creare transistor a effetto di campo (FET) più piccoli che presentano elevate efficienze energetiche.

I FET basati su nanotubi di carbonio hanno il potenziale per sovraperformare i transistor più piccoli basati sul silicio, ma il loro vantaggio nelle implementazioni nel mondo reale deve ancora essere definitivamente dimostrato. Un recente articolo di ricercatori dell'Università di Pechino e di altri istituti cinesi, pubblicato su Nature Electronics , delinea la realizzazione di FET basati su nanotubi di carbonio che possono essere scalati fino alle stesse dimensioni di un nodo tecnologico al silicio da 10 nm.

"I recenti progressi nella realizzazione di array di nanotubi di carbonio semiconduttori ad alta densità su scala wafer ci hanno portato un passo avanti verso l'uso pratico dei nanotubi di carbonio nei circuiti CMOS", ha detto a Phys.org Zhiyong Zhang, uno dei ricercatori che hanno condotto lo studio. "Tuttavia, gli sforzi di ricerca precedenti si sono concentrati principalmente sul ridimensionamento della lunghezza del canale o del gate dei transistor ai nanotubi di carbonio mantenendo grandi dimensioni di contatto, cosa che non può essere accettata per i circuiti CMOS ad alta densità nelle applicazioni pratiche.

"Il nostro obiettivo principale di questo lavoro è esplorare la vera capacità di scalabilità degli array di nanotubi di carbonio utilizzando due cifre di merito nell'industria del silicio, ovvero il passo del gate contattato e l'area della cella SRAM 6T, mantenendo i vantaggi prestazionali."

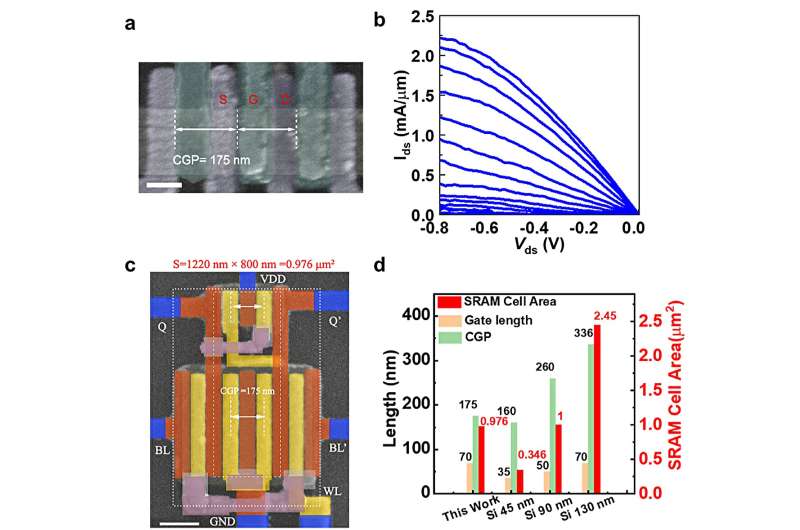

Zhang e i suoi colleghi si proponevano essenzialmente di dimostrare il valore pratico dei transistor ai nanotubi di carbonio, dimostrando che possono sovraperformare i FET convenzionali a base di silicio con un passo di gate comparabile e un'area della cella SRAM da 6T. Per raggiungere questo obiettivo, hanno prima fabbricato FET basati su array di nanotubi di carbonio con un passo di contatto di 175 nm. Questo passo del gate è stato realizzato ridimensionando la lunghezza del gate e la lunghezza del contatto rispettivamente a 85 nm e 80 nm.

"Sorprendentemente, i transistor hanno mostrato un'impressionante corrente di funzionamento di 2,24 mA/μm e una transconduttanza di picco di 1,64 mS/μm, superando le prestazioni elettroniche dei transistor con nodo in silicio da 45 nm", ha affermato Zhang. "Inoltre, la cella SRAM da 6T costituita da questi transistor nanotubi ultra-scalati è stata fabbricata entro 1 μm 2 e funziona correttamente. Abbiamo quindi studiato l'ostacolo principale, ovvero la resistenza di contatto dei transistor in nanotubi di carbonio per un ulteriore ridimensionamento."

Studi precedenti hanno dimostrato che quando si segue uno schema di contatto diffuso noto come “contatto laterale”, i portatori di carica possono essere iniettati solo dalla superficie dei nanotubi di carbonio. Ciò rende la resistenza della lunghezza dei nanotubi dipendente dalla lunghezza, limitando la misura in cui possono essere miniaturizzati.

Per superare questo problema, Zhang e i suoi colleghi hanno introdotto un nuovo schema che chiamano “contatto completo”. Questo schema prevede il taglio di entrambe le estremità dei nanotubi di carbonio prima di formare il contatto, che a sua volta consente di iniettare parte dei trasportatori da queste estremità.

"Questo nuovo schema di contatti consente ai transistor in nanotubi di carbonio di essere ulteriormente ridotti fino a un passo del gate contattato inferiore a 55 nm che corrisponde al nodo tecnologico di silicio da 10 nm, superando al contempo le prestazioni dei transistor in silicio con nodo da 10 nm grazie all'elevata mobilità dei portatori e alla velocità di Fermi", ha affermato Zhang. "Il nostro lavoro ha dimostrato sperimentalmente una vera tecnologia dei nodi da 90 nm utilizzando nanotubi di carbonio, che potrebbero essere resi geometricamente più piccoli e offrire prestazioni elettroniche superiori ai transistor dei nodi in silicio da 90 nm."

Questo recente articolo introduce un approccio affidabile ai transistor ai nanotubi di carbonio su scala ridotta, senza comprometterne le prestazioni. Finora, il team ha utilizzato la propria strategia per creare un transistor con nodo da 90 nm, ma riprogettando la struttura dei contatti ritengono che questi transistor potrebbero essere ridotti al di sotto di un nodo inferiore a 10 nm.

In futuro, il lavoro di Zhang e dei suoi colleghi potrebbe contribuire alla creazione di transistor basati su nanotubi di carbonio sempre più piccoli ed efficienti. Ciò potrebbe avere preziose implicazioni per lo sviluppo dell'elettronica.

"La prossima sfida che stiamo affrontando è quella di ridurre la geometria dei contatti per i transistor di tipo n in nanotubi di carbonio per costruire una tecnologia CMOS completa, che costituisce gli elementi costitutivi necessari per i moderni circuiti integrati digitali", ha aggiunto Zhang.

"Attualmente utilizziamo lo scandio per il contatto dei transistor ai nanotubi di carbonio di tipo n. Tuttavia, stiamo affrontando grandi difficoltà quando riduciamo la lunghezza del contatto a causa dell'ossidazione di questo metallo a bassa funzione di lavoro. Inoltre, stiamo lavorando per caratterizzare accuratamente la qualità dell'interfaccia tra gli array di nanotubi di carbonio e il dielettrico ad alto κ, migliorandola al livello dei transistor CMOS in silicio per migliorare la controllabilità e l'affidabilità del gate."

Ulteriori informazioni: Yanxia Lin et al, Ridimensionamento di transistor in nanotubi di carbonio allineati a un nodo inferiore a 10 nm, Nature Electronics (2023). DOI:10.1038/s41928-023-00983-3

Informazioni sul giornale: Elettronica naturale

© 2023 Rete Scienza X