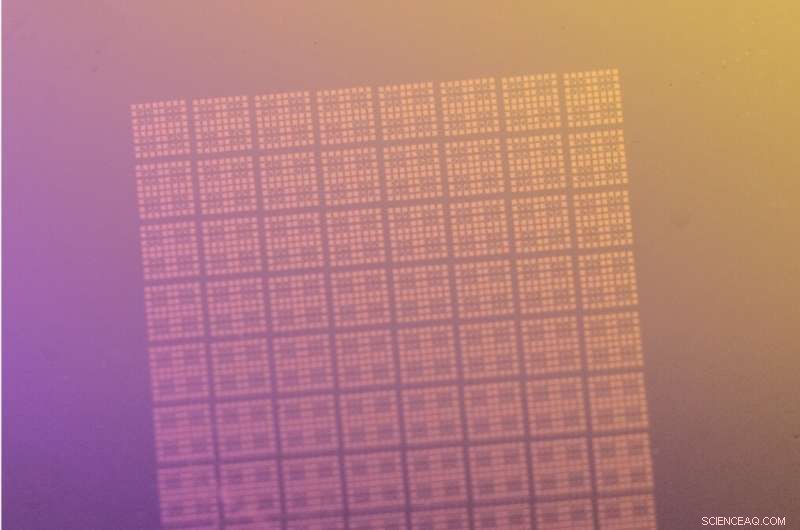

Immagine di un array di dispositivi fabbricato utilizzando il metodo proposto dai ricercatori. Credito:Li et al.

I semiconduttori 2-D potrebbero avere applicazioni molto utili, in particolare come materiali di canale per transistor a bassa potenza. Questi materiali mostrano una mobilità molto elevata a spessori estremi, il che li rende alternative particolarmente promettenti al silicio nella fabbricazione dell'elettronica.

Nonostante i loro vantaggi, l'implementazione di questi materiali nei transistor si è finora rivelata una sfida. Infatti, I semiconduttori 2-D sono di natura priva di legami penzolanti; così, è notoriamente difficile depositare dielettrici di gate ultrasottili ad alto κ (cioè, sostanze con proprietà dielettriche o isolanti) sui materiali tramite deposizione di strati atomici (ALD), spesso dando luogo a film discontinui.

I ricercatori della Nanjing University in Cina hanno recentemente presentato una nuova strategia per superare questa limitazione, consentendo infine la deposizione di dielettrici di gate su semiconduttori 2-D. In un articolo pubblicato su Elettronica della natura , hanno riportato il successo dell'ALD di dielettrici di gate ad alta su semiconduttori 2-D utilizzando un cristallo molecolare come strato di semina.

"La nostra ricerca cerca di risolvere il problema dell'integrazione dielettrica del gate di alta qualità per i transistor 2-D, "Xinran Wang, uno dei ricercatori che ha condotto lo studio, ha detto a TechXplore. "Nei transistor al Si di ultima generazione, lo spessore effettivo dell'ossido (EOT) è stato ridotto a sub-1 nm. Attualmente, c'è un grande divario tra i materiali 2-D e il Si in termini di EOT, densità dello stato dell'interfaccia (Dit), e perdita del cancello. Se si vuole portare avanti seriamente la tecnologia dei transistor 2-D, questo divario deve essere superato".

L'approccio introdotto da Wang e dai suoi colleghi consente la produzione di dielettrici con uno spessore di ossido equivalente di 1 nm su grafene, bisolfuro di molibdeno (MoS 2 ) e diseleniuro di tungsteno (WSe 2 ). I dielettrici che risultano dall'approccio dei ricercatori mostrano una rugosità ridotta, densità degli stati di interfaccia e di dispersione rispetto a quelli prodotti utilizzando metodi più convenzionali. interessante, presentano anche un campo di ripartizione migliorato.

"Oltre ai transistor 2-D, un'altra direzione esplorata dal mio gruppo di ricerca è l'elettronica organica, " Wang ha aggiunto. "Negli ultimi anni, abbiamo sviluppato mezzi per controllare con precisione l'assemblaggio delle molecole sulla superficie del materiale 2-D. Per molte molecole, compreso PTCDA, abbiamo dimostrato che possiamo controllare la crescita così bene che solo un monostrato (~0.3 nm) viene depositato uniformemente, con un'interfaccia molto pulita."

Lo strato di interfaccia creato da Wang e dal suo team di ricerca nel loro lavoro precedente è uno degli strati di interfaccia più sottili attualmente realizzabili. Nel loro presente studio, hanno usato questo strato per fabbricare transistor a radiofrequenza al grafene che funzionano a 60 GHz, così come MoS 2 e WSe 2 transistor metallo-ossido-semiconduttore complementari con una tensione di alimentazione di 0,8 V e una bassa oscillazione sottosoglia di 60 mV dec -1 . Finalmente, hanno anche usato la loro tecnica per creare MoS 2 transistor con una lunghezza del canale di 20 nm con un rapporto on/off di oltre 10 7 .

"Penso che il nostro risultato più significativo sia stato che siamo stati in grado di ottenere 1 nm EOT in materiali 2-D, " Wang ha detto. "È opinione diffusa che il canale 2-D possa ridurre il consumo energetico dei transistor rispetto ai semiconduttori di massa. Però, per raggiungere questo obiettivo, dobbiamo usare la stessa tensione di funzionamento, e i transistor possono essere spenti bruscamente (oscillazione sottosoglia vicino a 60 mV/dec). Entrambe le quantità dipendono fortemente dalla qualità e dallo spessore del dielettrico di gate. Il nostro studio dimostra veramente il potenziale dei semiconduttori 2-D verso l'elettronica a bassa potenza".

Wang e il suo gruppo di ricerca sono stati i primi a sviluppare con successo transistor 2-D con EOT da 1 nm, deponendo con successo il dielettrico su tre diversi materiali. Sorprendentemente, l'EOT e la dispersione di gate che hanno ottenuto sono paragonabili a quelli osservati nei CMOS di silicio allo stato dell'arte, che rappresenta un significativo passo avanti in questo settore di ricerca.

"Penso che ci sia ancora molto margine di miglioramento, " Wang ha detto. "Per esempio, Il Dit nei transistor 2-D è ancora ~2 ordini di grandezza superiore al Si CMOS. Inoltre, sarebbe bello ridurre ulteriormente l'EOT a ~ 0,8 nm utilizzando ossidi a k più alto. Finalmente, resta da studiare anche la compatibilità dei materiali che abbiamo sviluppato con i processi CMOS esistenti."

© 2020 Scienza X Rete