Il team NUS Green IC:Dr Orazio Aiello (a sinistra) e il Professore Associato Massimo Alioto (a destra). Credito:Università Nazionale di Singapore

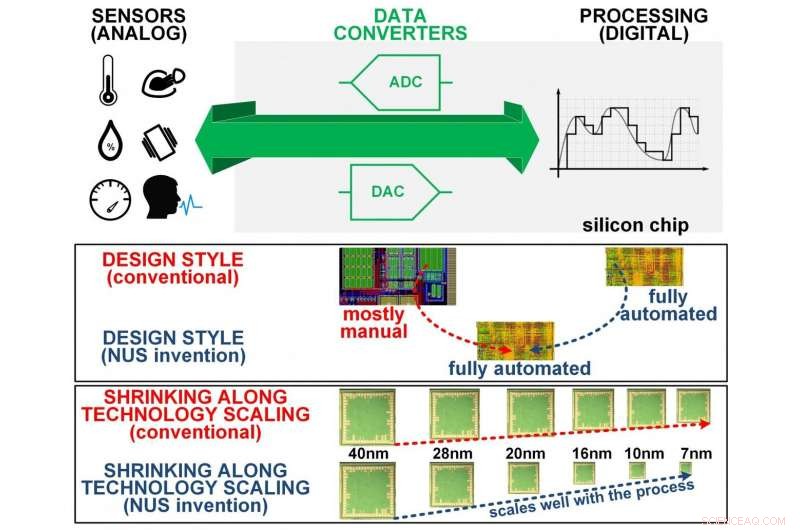

Il gruppo di ricerca Green IC del Dipartimento di Ingegneria Elettrica e Informatica della Facoltà di Ingegneria dell'Università Nazionale di Singapore (NUS) ha inventato una nuova classe di convertitori da digitale ad analogico (DAC) e da analogico a digitale (ADC) che possono essere interamente progettato con una metodologia di progettazione digitale completamente automatizzata, grazie alla sua architettura completamente digitale (Fig. 1).

Rispetto alle tradizionali architetture e metodologie analogiche, il tempo di completamento della progettazione per queste nuove interfacce di sensori è ridotto da mesi a ore. La drastica riduzione dello sforzo di progettazione è molto vantaggiosa nei sistemi al silicio sensibili ai costi, come i sensori per l'Internet of Things (IoT). La nuova architettura del convertitore di dati ha anche una complessità molto bassa, riducendo l'area di silicio e quindi il costo di produzione di almeno 30 volte, rispetto ai modelli convenzionali.

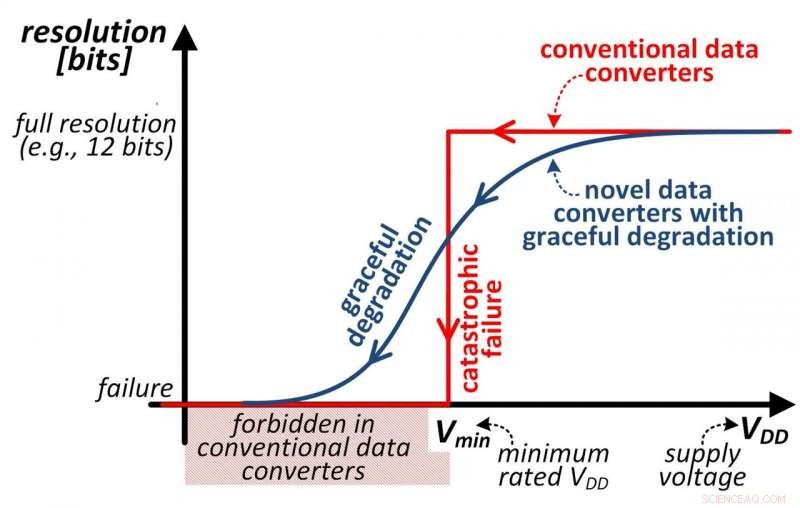

Questi nuovi convertitori di dati mostrano anche la capacità senza precedenti di degradare con grazia la fedeltà del segnale quando la sua tensione di alimentazione o la frequenza di clock subiscono ampie fluttuazioni (Fig. 2). Tali fluttuazioni sono comuni nei sensori IoT ad energia raccolta, essendo che la potenza raccolta dall'ambiente circostante (ad es. cella solare) è altamente irregolare. A sua volta, ciò consente il monitoraggio ininterrotto del segnale del sensore anche in condizioni di potenza raccolta sfavorevoli, e senza regolazione della tensione. Anziché, i convertitori di dati tradizionali soffrono di un catastrofico degrado della risoluzione quando la tensione di alimentazione è inferiore al suo valore nominale minimo Vmin (o la frequenza supera il suo valore nominale massimo) come in Fig. 2, quindi necessitano di circuiti affamati di energia per la regolazione della tensione e della frequenza.

La ricerca è stata condotta in collaborazione con il Professore Associato Paolo Crovetti del Politecnico di Torino in Italia, ed è supportato dal Ministero della Pubblica Istruzione di Singapore e dalla Commissione Europea.

Interfacce sensore più piccole, più semplice e veloce da progettare

"La nostra ricerca trasforma la progettazione tradizionalmente analogica e per lo più manuale di convertitori di dati in progettazione digitale completamente automatizzata, riducendo l'area di silicio di un ordine di grandezza e il tempo di progettazione di due ordini di grandezza, consentendo alle aziende di semiconduttori di essere competitive in termini di costi raggiungendo i mercati più rapidamente, " ha affermato il capogruppo Professore Associato Massimo Alioto, che proviene dal Dipartimento di Ingegneria Elettrica e Informatica presso la Facoltà di Ingegneria NUS.

L'errore catastrofico è sostituito da un grazioso degrado della risoluzione nella nuova classe di convertitori di dati convenzionali inventati dal team NUS. Questo permette di semplificare drasticamente la progettazione del sistema, sopprimendo la necessità di un'accurata regolazione della tensione. Credito:Università Nazionale di Singapore

Ha aggiunto, "Essere digitale, le nostre interfacce dei sensori sono facilmente trasferibili tra tecnologie e applicazioni di produzione, e possono essere immersi in circuiti digitali per evitare il tradizionale sforzo richiesto dalla loro integrazione sullo stesso chip di silicio." (Fig. 1).

Il team NUS ha dimostrato il concetto attraverso diversi chip di silicio che implementano sia DAC che ADC con un'area estremamente bassa. Come esempio, è stato dimostrato un DAC a 12 bit prodotto con tecnologia CMOS standard a 40 nm con un'area pari al diametro di una ciocca di capelli umani. La sua intrinseca suscettibilità al ridimensionamento della tecnologia lo fa rimpicciolire di circa altre 32 volte se implementato nella tecnologia attualmente migliore (7 nm).

Allo stesso tempo, l'invenzione NUS ha dimostrato di consentire convertitori di dati con risoluzioni elevate (fino a 16 bit), pur ottenendo semplicità progettuale e compattezza.

Membro del team Dott. Orazio Aiello, che è visiting research fellow presso il Dipartimento, disse, "Il nostro team ha introdotto un nuovo paradigma di design che ci avvicina alla visione definitiva di poco costoso, dispositivi IoT tecnologicamente scalabili e ultracompatti."

Una robustezza senza precedenti porta ulteriori vantaggi a livello di sistema

L'innovazione NUS semplifica ulteriormente la progettazione del sistema integrato, sfruttando la capacità senza precedenti di resistere a fluttuazioni di tensione e frequenza molto consistenti, rilassando così i requisiti di precisione nella generazione di tensione e frequenza.

Un guasto catastrofico è sostituito da una graziosa degradazione della risoluzione nella nuova classe di convertitori di dati convenzionali inventati dai ricercatori NUS. Credito:Università Nazionale di Singapore

Infatti, i convertitori di dati convenzionali che funzionano a una tensione di alimentazione inferiore al valore nominale minimo (o a una frequenza di clock eccessiva) subiscono un guasto catastrofico, e quindi non riesce a svolgere la sua funzione prevista (Fig. 2). Anzi, gli innovativi convertitori di dati inventati dal team NUS mostrano un grazioso degrado della risoluzione e della fedeltà del segnale quando la tensione di alimentazione o la frequenza di clock superano l'intervallo consentito. Come esempio, è stato dimostrato che un DAC progettato per 1 V funziona correttamente a metà di questa tensione, mentre degrada la sua risoluzione di solo 1 bit quando la tensione di alimentazione viene ridotta di un sostanziale 0,3V.

Assoc Prof Alioto ha detto, "La capacità di avere un discreto degrado della risoluzione in caso di sovrascalatura di tensione e frequenza elimina la necessità di soluzioni circuitali complesse che regolino con precisione la tensione di alimentazione e la frequenza di clock utilizzate dai convertitori di dati. In altre parole, i nostri convertitori di dati sono più semplici da progettare, e anche semplificare il sistema in cui sono impiegati."

Prossimi passi

Il team sta attualmente lavorando su un nuovo paradigma che trasforma i sottosistemi di silicio tradizionalmente analogici e ad alta intensità di progettazione in progetti basati su celle digitali standard supportati da flussi di progettazione completamente automatizzati, spingendo i confini del classico design digitalmente assistito. Questo studio di ricerca coinvolge diversi sottosistemi fondamentali come amplificatori, oscillatori, riferimenti di tensione e corrente, e molti altri.

Il team di ricerca mira a trasformare il modo in cui sono progettati i sistemi integrati, consentendo ultrarapida, progettazione ultracompatta e tecnologicamente portatile di interi sistemi.