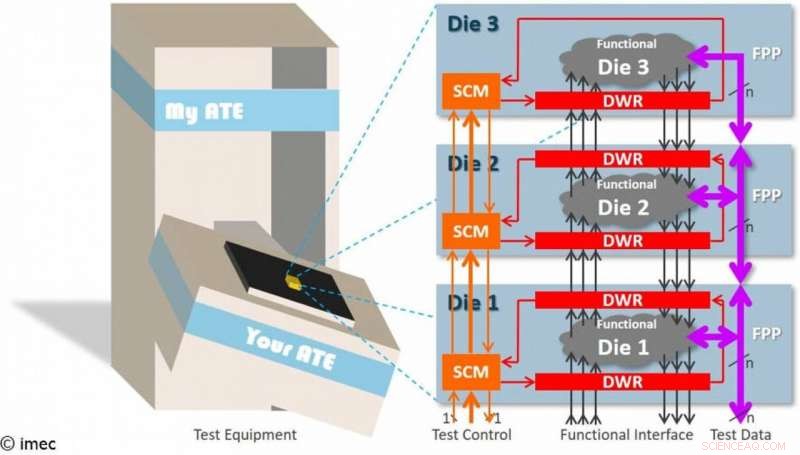

Sezione trasversale concettuale di un 3D-IC costituito da tre stampi impilati. Le apparecchiature di test inviano stimoli di test e ricevono risposte di test dall'interfaccia esterna del 3D-IC situata nella parte inferiore dello stack. Gli elementi design-for-test IEEE Std 1838™-2019 nei vari die formano un'architettura di accesso ai test coerente attraverso la quale l'apparecchiatura di test può accedere a ogni die nello stack. Credito:IMEC

Questa settimana, IMEC, un polo di ricerca e innovazione leader a livello mondiale nella nanoelettronica e nelle tecnologie digitali, ha annunciato che IEEE Std 1838TM-2019, recentemente approvato dalla IEEE Standards Association, sarà incluso nella IEEE Xplore Digital Library a partire da febbraio 2020. Il nuovo standard consente ai produttori di stampi di progettare stampi che, se conforme a questo standard, costituire, una volta impilato in un 3-D-IC da un integratore di stack, un'architettura di accesso di prova a livello di stack coerente. Lo sforzo di standardizzazione del 3-D-DfT (design-for-test) è stato avviato da IMEC.

I 3-D-IC sfruttano la dimensione verticale per un'ulteriore integrazione impilando gli stampi uno sopra l'altro come un modo per mantenere lo slancio della legge di Moore in corso. Eric Beyne, borsista e direttore del programma 3-D System Integration presso IMEC, dice, "I progressi nella lavorazione dei wafer e nelle tecnologie di assemblaggio stack stanno creando una ricchezza di diverse architetture stack. Ciò causa un forte aumento del numero di potenziali momenti in cui possono essere eseguiti i test per i difetti di fabbricazione:pre-bond (prima dell'impilamento), mid-bond (su stack parziali), post-bond (su pile complete), e test finale (su CI 3-D confezionati). L'apparecchiatura di test contatta i circuiti integrati tramite la sua interfaccia esterna tramite gli aghi della sonda o la presa di test. In una pila di matrici, quell'interfaccia esterna risiede tipicamente nel die inferiore dello stack. Affinché l'apparecchiatura di test sia in grado di fornire stimoli di test e ricevere risposte dai vari stampi nello stack, è necessaria la collaborazione degli stampi sottostanti per fornire l'accesso di prova allo stampo attualmente in fase di test."

Un gruppo di lavoro IEEE per standardizzare 3-D-DfT è stato fondato nel 2011 da Erik Jan Marinissen, direttore scientifico dell'IMEC di Lovanio, Belgio e ne è stato il primo presidente. Negli ultimi anni, Adam Cron, ingegnere principale di ricerca e sviluppo nel gruppo di progettazione di Synopsys, è stata la forza trainante in quanto attuale presidente del gruppo di lavoro.

Amit Sanghani, vicepresidente dell'ingegneria nel Design Group di Synopsys a Mountain View, California, Gli Stati Uniti hanno dichiarato:"Il 3-D-IC è una tecnologia importante per fornire la prossima ondata di innovazione mentre l'industria supera i 7 nm. Attualmente, die potrebbe provenire da diversi fornitori con architetture DfT disgiunte.

Il nuovo standard si compone di tre elementi principali. (1) DWR, il registro dell'involucro dello stampo:scansiona le catene al confine di ciascun die nella pila per consentire il test modulare delle parti interne di ciascun die e delle interconnessioni tra ciascuna coppia di die adiacenti. (2) SCM, il meccanismo di controllo seriale:un meccanismo di controllo del test a bit singolo che trasporta le istruzioni nello stack per controllare le modalità di test dei vari wrapper die. (3) FPP, la porta parallela flessibile opzionale, cioè., un meccanismo scalabile di accesso ai test multi-bit per trasportare in modo efficiente su e giù nello stack di stampi i grandi volumi di dati tipicamente associati ai test di produzione. Mentre DWR e SCM si basano sugli standard DfT esistenti, il FPP è veramente nuovo per IEEE Std 1838.

Wolfgang Meyer, direttore senior del gruppo R&D presso Cadence Design Systems a San Jose, California, NOI., dice, "Uno standard DfT come IEEE Std 1838 è importante per il settore. I produttori di stampi sanno cosa devono fornire, e gli integratori di stack sanno cosa possono aspettarsi. Inoltre, I fornitori di EDA come Cadence possono concentrare il proprio supporto di strumenti su architetture conformi al nuovo standard. È positivo che ci sia una certa scalabilità definita dall'utente con lo standard poiché il campo 3-D-IC è così ampio che uno standard rigido "taglia unica" non funzionerebbe".

Junlin Huang, manager di un team DfT forte di 150 persone di HiSilicon a Shenzhen, Cina, dice, "Per anno, effettuiamo l'inserimento DfT e la generazione automatica di modelli di test (ATPG) per decine di progetti di chip digitali molto grandi e complessi nelle tecnologie più avanzate. Ora, questi prodotti iniziano a utilizzare la tecnologia 3D e il mio team DfT deve essere pronto a gestire le sfide DfT e ATPG associate. IEEE Std 1838 ci aiuterà in questo compito."

Da febbraio 2020 in poi, il nuovo standard IEEE Std 1838 sarà disponibile tramite IEEE Xplore per gli abbonati agli standard IEEE e per l'acquisto a tutti gli altri.