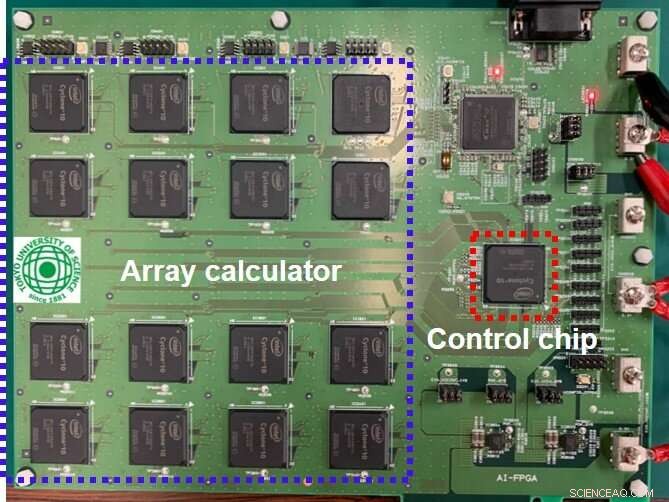

In un nuovo studio, i ricercatori di TUS, in Giappone, hanno proposto un processore di ricottura scalabile completamente connesso che, se implementato in FPGA, può facilmente superare le prestazioni di una moderna CPU nella risoluzione di vari problemi di ottimizzazione combinatoria in termini di velocità e consumo energetico. Il metodo proposto raggiunge questo obiettivo utilizzando un "calcolatore di array", costituito da più chip accoppiati e un "chip di controllo". Potrebbe essere applicato per risolvere problemi di ottimizzazione complessi simili nella logistica, nell'instradamento della rete, nella gestione del magazzino, nell'assegnazione del personale, nella consegna dei farmaci e nella scienza dei materiali. Credito:Takayuki Kawahara da TUS, Giappone

Ti è mai capitato di dover affrontare un problema in cui dovevi trovare una soluzione ottimale tra molte opzioni possibili, come trovare il percorso più rapido per un determinato luogo, considerando sia la distanza che il traffico?

Se è così, il problema che stavi affrontando è quello che è formalmente noto come "problema di ottimizzazione combinatoria". Sebbene formulati matematicamente, questi problemi sono comuni nel mondo reale e sorgono in diversi campi, tra cui logistica, routing di rete, apprendimento automatico e scienza dei materiali.

Tuttavia, i problemi di ottimizzazione combinatoria su larga scala sono molto impegnativi dal punto di vista computazionale da risolvere utilizzando computer standard, costringendo i ricercatori a rivolgersi ad altri approcci. Uno di questi approcci si basa sul "modello Ising", che rappresenta matematicamente l'orientamento magnetico degli atomi, o "spin", in un materiale ferromagnetico.

Ad alte temperature, questi spin atomici sono orientati in modo casuale. Ma quando la temperatura diminuisce, gli spin si allineano per raggiungere lo stato energetico minimo in cui l'orientamento di ogni spin dipende dai suoi vicini. Si scopre che questo processo, noto come "ricottura", può essere utilizzato per modellare problemi di ottimizzazione combinatoria in modo tale che lo stato finale degli spin produca la soluzione ottimale.

In un nuovo studio, i ricercatori di TUS, in Giappone, hanno proposto un processore di ricottura scalabile completamente connesso che, se implementato in FPGA, può facilmente superare le prestazioni di una moderna CPU nella risoluzione di vari problemi di ottimizzazione combinatoria in termini di velocità e consumo energetico. Il metodo proposto raggiunge questo obiettivo utilizzando un "calcolatore di array", costituito da più chip accoppiati e un "chip di controllo". Potrebbe essere applicato per risolvere problemi di ottimizzazione complessi simili nella logistica, nell'instradamento della rete, nella gestione del magazzino, nell'assegnazione del personale, nella consegna dei farmaci e nella scienza dei materiali. Credito:Takayuki Kawahara da TUS, Giappone

I ricercatori hanno provato a creare processori di ricottura che imitano il comportamento degli spin utilizzando dispositivi quantistici e hanno tentato di sviluppare dispositivi a semiconduttore utilizzando la tecnologia di integrazione su larga scala (LSI) con l'obiettivo di fare lo stesso. In particolare, il gruppo di ricerca del professor Takayuki Kawahara presso la Tokyo University of Science (TUS) in Giappone ha compiuto importanti progressi in questo particolare campo.

Nel 2020, il Prof. Kawahara e i suoi colleghi hanno presentato alla conferenza internazionale del 2020, IEEE SAMI 2020, uno dei primi processori di ricottura LSI completamente accoppiati (ovvero, che tiene conto di tutte le possibili interazioni spin-spin invece delle interazioni con i soli spin vicini), composto da 512 giri completamente collegati.

Il loro lavoro è apparso sulla rivista IEEE Transactions on Circuits and Systems I:Regular Papers . Questi sistemi sono notoriamente difficili da implementare e potenziare a causa dell'enorme numero di connessioni tra gli spin che devono essere considerati. Sebbene l'utilizzo di più chip completamente connessi in parallelo fosse una potenziale soluzione al problema della scalabilità, ciò rendeva proibitivo il numero richiesto di interconnessioni (cavi) tra i chip.

In un recente studio pubblicato su Microprocessori e Microsistemi , il Prof. Kawahara e il suo collega hanno dimostrato una soluzione intelligente a questo problema. Hanno sviluppato un nuovo metodo in cui il calcolo dello stato energetico del sistema è diviso prima tra più chip completamente accoppiati, formando un "calcolatore di array".

Un secondo tipo di chip, chiamato "chip di controllo", raccoglie quindi i risultati dal resto dei chip e calcola l'energia totale, che viene utilizzata per aggiornare i valori degli spin simulati. "Il vantaggio del nostro approccio è che la quantità di dati trasmessi tra i chip è estremamente ridotta", spiega il prof. Kawahara. "Sebbene il suo principio sia semplice, questo metodo ci consente di realizzare un sistema LSI scalabile e completamente connesso per risolvere problemi di ottimizzazione combinatoria attraverso la ricottura simulata."

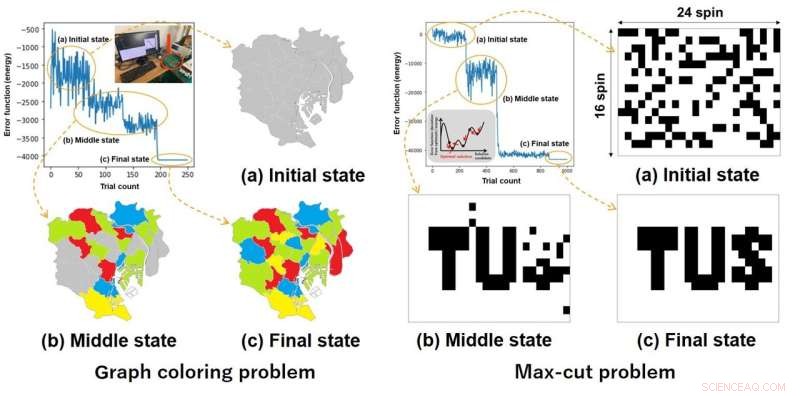

I ricercatori hanno implementato con successo il loro approccio utilizzando chip FPGA commerciali, che sono dispositivi a semiconduttore programmabili ampiamente utilizzati. Hanno costruito un sistema di ricottura completamente connesso con 384 giri e lo hanno utilizzato per risolvere diversi problemi di ottimizzazione, tra cui un problema di colorazione del grafico a 92 nodi e un problema di taglio massimo a 384 nodi.

Ancora più importante, questi esperimenti di prova di concetto hanno mostrato che il metodo proposto porta veri vantaggi in termini di prestazioni. Rispetto a una moderna CPU standard che modella lo stesso sistema di ricottura, l'implementazione FPGA è stata 584 volte più veloce e 46 volte più efficiente dal punto di vista energetico quando ha risolto il problema del taglio massimo.

Ora, con questa dimostrazione di successo del principio di funzionamento del loro metodo in FPGA, i ricercatori hanno in programma di portarlo al livello successivo. "Desideriamo produrre un chip LSI progettato su misura per aumentare la capacità e migliorare notevolmente le prestazioni e l'efficienza energetica del nostro metodo", afferma il prof. Kawahara. "Questo ci consentirà di realizzare le prestazioni richieste nei campi dello sviluppo di materiali e della scoperta di farmaci, che comportano problemi di ottimizzazione molto complessi."

Infine, il Prof. Kawahara nota che desidera promuovere l'implementazione dei loro risultati per risolvere problemi reali nella società. Il suo gruppo spera di impegnarsi in una ricerca congiunta con le aziende e portare il loro approccio al cuore della tecnologia di progettazione dei semiconduttori, aprendo le porte alla rinascita dei semiconduttori in Giappone. + Esplora ulteriormente