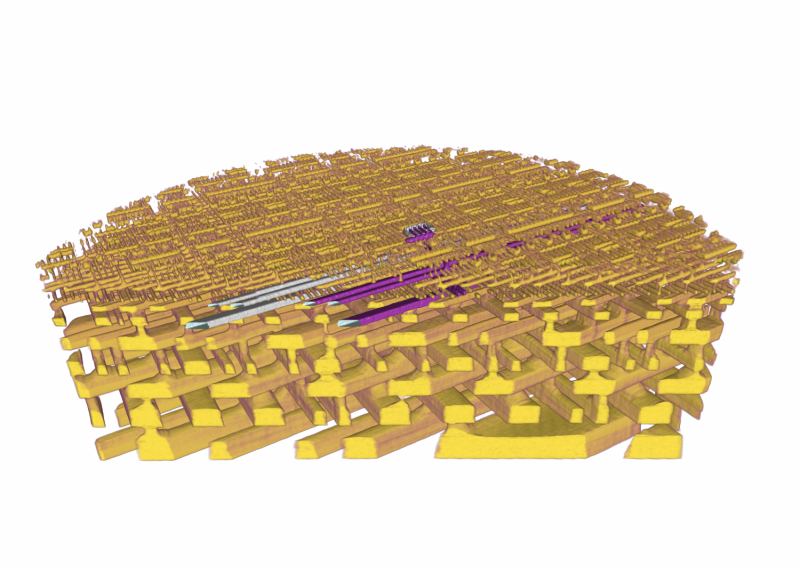

Rappresentazione 3D della struttura interna di un microchip (un processore Intel). La vista mostrata è esattamente al livello in cui si trovano i transistor. Il materiale in giallo è rame, che mostra le connessioni del circuito del processore che collegano i singoli transistor tra loro. Illustrare, sono state colorate alcune interconnessioni le cui linee potrebbero essere seguite nel volume esaminato. Le linee mostrate singolarmente sono larghe circa 45 nanometri (45 milionesimi di millimetro); in tutto, è stato esaminato un pezzo del processore di circa 10 micrometri (10 millesimi di millimetro) di diametro. Credito:Istituto Paul Scherrer/Mirko Holler

I ricercatori del Paul Scherrer Institute PSI hanno realizzato immagini 3D dettagliate di un chip per computer disponibile in commercio. Questo segna la prima volta che un metodo non distruttivo ha visualizzato i percorsi del cablaggio interno di un chip (appena 45 nanometri—45 milionesimi di millimetro—largo) e dei suoi transistor alti 34 nanometri chiaramente senza distorsioni o deformazioni. È una grande sfida per i produttori determinare se, alla fine, la struttura dei loro chip è conforme alle specifiche. Questi risultati rappresentano quindi un'importante applicazione di un metodo di tomografia a raggi X che i ricercatori del PSI stanno sviluppando da diversi anni. Nel loro esperimento, i ricercatori hanno esaminato un piccolo pezzo che avevano ritagliato dal chip in anticipo. Questo campione è rimasto intatto durante la misurazione. L'obiettivo ora è estendere il metodo in modo tale da poter essere utilizzato per esaminare chip completi. I ricercatori hanno condotto gli esperimenti presso la Swiss Light Source SLS dell'Istituto Paul Scherrer.

Riportano i loro risultati nell'ultima edizione della rivista Natura .

Il cablaggio elettrico in molti dei chip elettronici dei nostri computer e telefoni cellulari è largo solo 45 nanometri, i transistor alti 34 nanometri. Sebbene oggi sia pratica standard produrre strutture così delicate, rimane una sfida misurare in dettaglio l'esatta struttura di un truciolo finito per verificare, Per esempio, se è costruito secondo le specifiche. Oggi, per tali esami, i produttori utilizzano principalmente un metodo in cui viene rimosso strato dopo strato del chip e quindi, dopo ogni passo, la superficie viene esaminata al microscopio elettronico; questo è noto come imaging al microscopio elettronico a scansione FIB/SEM - fascio ionico focalizzato.

Ora i ricercatori del Paul Scherrer Institute PSI hanno utilizzato i raggi X per ottenere immagini 3D non distruttive di un chip, in modo che i percorsi delle linee conduttrici e le posizioni dei singoli transistor e degli altri elementi circuitali diventassero chiaramente visibili. La risoluzione dell'immagine che siamo stati in grado di produrre è paragonabile al metodo di esame FIB/SEM convenzionale, spiega Mirko Holler, capofila del progetto. Ma siamo stati in grado di evitare due svantaggi significativi:in primo luogo, il campione è rimasto intatto, e abbiamo informazioni complete sulla struttura tridimensionale. In secondo luogo, abbiamo evitato distorsioni delle immagini che si verificano in FIB/SEM se la superficie della singola fetta non è esattamente planare.

Posizionato con precisione nanometrica

Per il loro studio, i ricercatori hanno utilizzato uno speciale metodo tomografico (pticotomografia) che hanno sviluppato e migliorato nel corso degli ultimi anni, e che oggi offre la migliore risoluzione mondiale di 15 nanometri (15 milionesimi di millimetro) per l'esame di un volume relativamente grande. Nell'esperimento l'oggetto da studiare viene sottoposto a raggi X in punti precisamente determinati con la luce della Swiss Light Source SLS dell'Istituto Paul Scherrer:per ogni punto illuminato un rivelatore misura quindi il modello di luce dei raggi X dopo il suo passaggio attraverso il campione . Il campione viene quindi ruotato a piccoli passi e quindi sottoposto a raggi X di nuovo gradualmente dopo ogni giro. Dall'insieme dei dati ottenuti, è possibile determinare la struttura tridimensionale del campione. Con queste misurazioni, la posizione del campione deve essere nota con una precisione di pochi nanometri:questa è stata una delle sfide particolari nell'allestimento della nostra stazione sperimentale, dice Holler.

Nel loro esperimento i ricercatori hanno esaminato piccoli pezzi di due chip:un chip rivelatore sviluppato al PSI e un chip per computer disponibile in commercio. Ogni pezzo era di circa 10 micrometri (cioè, 10 millesimi di millimetro). Sebbene l'esame di un intero chip con l'attuale configurazione di misurazione non sia possibile, i vantaggi del metodo si manifestano anche in questa forma, cosicché i primi potenziali utilizzatori hanno già manifestato interesse a condurre misurazioni presso il PSI.

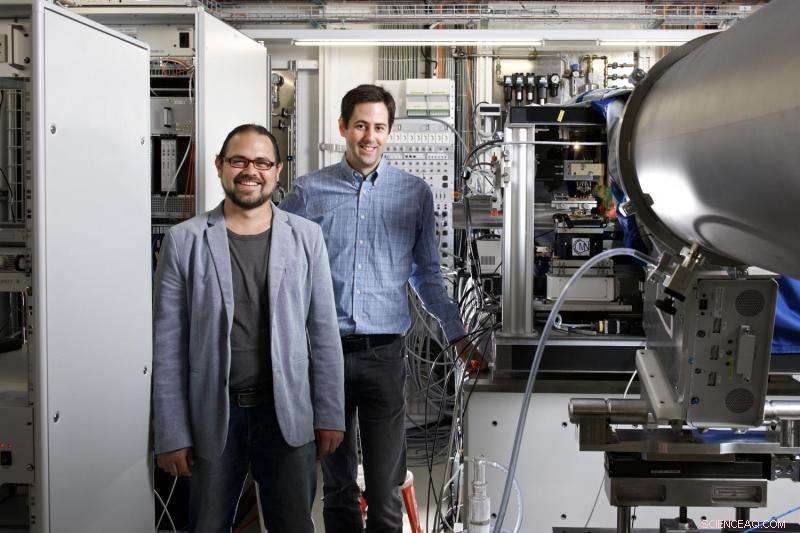

I ricercatori del PSI Mirko Holler (a destra) e Manuel Guizar-Sicairos alla linea di luce cSAXS della Swiss Light Source SLS dell'Istituto Paul Scherrer. Qui hanno reso visibile la struttura tridimensionale di un microchip. Credito:Istituto Paul Scherrer/Markus Fischer

L'obiettivo:esaminare interi microchip

Attualmente stiamo iniziando ad estendere il metodo in modo tale che possa essere utilizzato per esaminare interi microchip entro un tempo di misurazione accettabile. Quindi sarà anche possibile studiare più volte la stessa area di un chip, ad esempio per osservare come cambia sotto influenze esterne, spiega Gabriele Aeppli, capo della Divisione Radiazioni di Sincrotrone e Nanotecnologie del PSI.

Una seconda rappresentazione 3D della struttura interna di un microchip (un processore Intel). Credito:Istituto Paul Scherrer/Mirko Holler