Un nuovo design del chip fotonico riduce drasticamente l'energia necessaria per calcolare con la luce, con simulazioni che suggeriscono che potrebbe eseguire reti neurali ottiche 10 milioni di volte in modo più efficiente rispetto alle sue controparti elettriche. Credito:MIT News

I ricercatori del MIT hanno sviluppato un nuovo chip "fotonico" che utilizza la luce invece dell'elettricità e consuma relativamente poca energia nel processo. Il chip potrebbe essere utilizzato per elaborare enormi reti neurali milioni di volte in modo più efficiente rispetto ai computer classici di oggi.

Le reti neurali sono modelli di apprendimento automatico ampiamente utilizzati per attività come l'identificazione di oggetti robotici, elaborazione del linguaggio naturale, sviluppo di farmaci, imaging medico, e l'alimentazione di auto senza conducente. Nuove reti neurali ottiche, che utilizzano fenomeni ottici per accelerare il calcolo, possono funzionare molto più velocemente e in modo più efficiente rispetto alle loro controparti elettriche.

Ma poiché le reti neurali tradizionali e ottiche diventano più complesse, consumano tonnellate di energia. Per affrontare questo problema, ricercatori e importanti aziende tecnologiche, tra cui Google, IBM, e Tesla, hanno sviluppato "acceleratori di intelligenza artificiale, " chip specializzati che migliorano la velocità e l'efficienza dell'addestramento e del test delle reti neurali.

Per i chip elettrici, compresa la maggior parte degli acceleratori di intelligenza artificiale, esiste un limite minimo teorico per il consumo di energia. Recentemente, I ricercatori del MIT hanno iniziato a sviluppare acceleratori fotonici per reti neurali ottiche. Questi chip eseguono ordini di grandezza in modo più efficiente, ma si basano su alcuni componenti ottici ingombranti che limitano il loro utilizzo a reti neurali relativamente piccole.

In un articolo pubblicato su Revisione fisica X , I ricercatori del MIT descrivono un nuovo acceleratore fotonico che utilizza componenti ottici più compatti e tecniche di elaborazione del segnale ottico, per ridurre drasticamente sia il consumo energetico che l'area del chip. Ciò consente al chip di adattarsi a reti neurali di diversi ordini di grandezza più grandi delle sue controparti.

L'addestramento simulato delle reti neurali sul set di dati di classificazione delle immagini MNIST suggerisce che l'acceleratore può teoricamente elaborare reti neurali più di 10 milioni di volte al di sotto del limite di consumo energetico degli acceleratori elettrici tradizionali e circa 1, 000 volte al di sotto del limite degli acceleratori fotonici. I ricercatori stanno ora lavorando su un prototipo di chip per dimostrare sperimentalmente i risultati.

"Le persone sono alla ricerca di una tecnologia in grado di calcolare oltre i limiti fondamentali del consumo di energia, "dice Ryan Hamerly, un postdoc nel Laboratorio di Ricerca di Elettronica. "Gli acceleratori fotonici sono promettenti... ma la nostra motivazione è costruire un [acceleratore fotonico] in grado di scalare fino a grandi reti neurali".

Le applicazioni pratiche per tali tecnologie includono la riduzione del consumo energetico nei data center. "C'è una crescente domanda di data center per l'esecuzione di grandi reti neurali, e sta diventando sempre più computazionalmente intrattabile man mano che la domanda cresce, " afferma il coautore Alexander Sludds, uno studente laureato nel Laboratorio di Ricerca di Elettronica. L'obiettivo è "soddisfare la domanda computazionale con l'hardware della rete neurale... per affrontare il collo di bottiglia del consumo energetico e della latenza".

Ad unirsi a Sludds e Hamerly sulla carta sono:la co-autrice Liane Bernstein, uno studente laureato RLE; Marin Soljacic, un professore di fisica del MIT; e Dirk Englund, professore associato di ingegneria elettrica e informatica al MIT, un ricercatore in RLE, e capo del Laboratorio di Fotonica Quantistica.

Design compatto

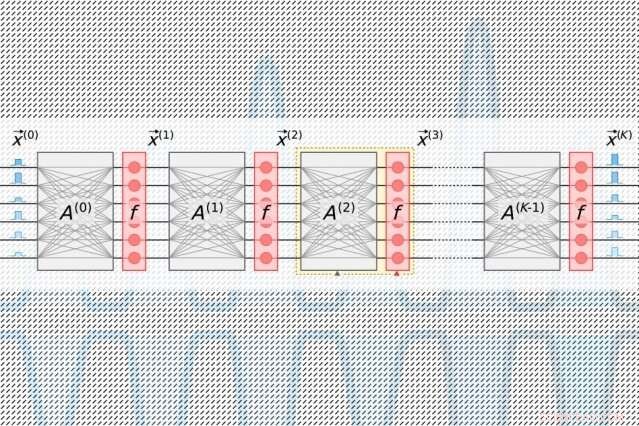

Le reti neurali elaborano i dati attraverso molti livelli computazionali contenenti nodi interconnessi, chiamati "neuroni, " per trovare modelli nei dati. I neuroni ricevono input dai loro vicini a monte e calcolano un segnale di uscita che viene inviato ai neuroni più a valle. Ad ogni input viene inoltre assegnato un "peso, " un valore basato sulla sua importanza relativa a tutti gli altri input. Man mano che i dati si propagano "più in profondità" attraverso i livelli, la rete apprende informazioni progressivamente più complesse. Alla fine, un livello di output genera una previsione basata sui calcoli in tutti i livelli.

Tutti gli acceleratori di intelligenza artificiale mirano a ridurre l'energia necessaria per elaborare e spostare i dati durante uno specifico passaggio di algebra lineare nelle reti neurali, chiamato "moltiplicazione di matrici". Là, neuroni e pesi sono codificati in tabelle separate di righe e colonne e quindi combinati per calcolare gli output.

Negli acceleratori fotonici tradizionali, laser a impulsi codificati con informazioni su ciascun neurone in uno strato fluiscono nelle guide d'onda e attraverso i divisori di raggio. I segnali ottici risultanti vengono immessi in una griglia di componenti ottici quadrati, chiamati "interferometri di Mach-Zehnder, " che sono programmati per eseguire la moltiplicazione di matrici. Gli interferometri, che sono codificati con informazioni su ciascun peso, utilizzare tecniche di interferenza del segnale che elaborano i segnali ottici e i valori di peso per calcolare un output per ciascun neurone. Ma c'è un problema di scala:per ogni neurone deve esserci una guida d'onda e, per ogni peso, ci deve essere un interferometro. Poiché il numero di pesi quadrati con il numero di neuroni, quegli interferometri occupano molto spazio.

"Ti rendi subito conto che il numero di neuroni di input non può mai essere maggiore di 100 o giù di lì, perché non puoi inserire così tanti componenti sul chip, " Dice Hamerly. "Se il tuo acceleratore fotonico non può elaborare più di 100 neuroni per strato, quindi rende difficile implementare grandi reti neurali in quell'architettura".

Il chip dei ricercatori si basa su un più compatto, schema "optoelettronico" ad alta efficienza energetica che codifica i dati con segnali ottici, ma utilizza il "rilevamento bilanciato dell'omodina" per la moltiplicazione della matrice. Questa è una tecnica che produce un segnale elettrico misurabile dopo aver calcolato il prodotto delle ampiezze (altezza d'onda) di due segnali ottici.

Gli impulsi di luce codificati con le informazioni sui neuroni di input e output per ogni livello della rete neurale, necessari per addestrare la rete, fluiscono attraverso un singolo canale. Impulsi separati codificati con le informazioni di intere righe di pesi nella tabella di moltiplicazione della matrice fluiscono attraverso canali separati. I segnali ottici che trasportano il neurone ei dati sul peso si estendono a ventaglio verso la griglia di fotorivelatori omodini. I fotorivelatori utilizzano l'ampiezza dei segnali per calcolare un valore di uscita per ciascun neurone. Ogni rivelatore alimenta un segnale elettrico di uscita per ogni neurone in un modulatore, che riconverte il segnale in un impulso luminoso. Quel segnale ottico diventa l'input per il livello successivo, e così via.

Il progetto richiede un solo canale per neurone di input e output, e solo tanti fotorivelatori omodini quanti sono i neuroni, non pesi. Poiché ci sono sempre molti meno neuroni che pesi, questo consente di risparmiare spazio significativo, quindi il chip è in grado di scalare fino a reti neurali con più di un milione di neuroni per strato.

Trovare il punto debole

Con acceleratori fotonici, c'è un rumore inevitabile nel segnale. Più luce viene alimentata nel chip, minore è il rumore e maggiore è la precisione, ma ciò diventa piuttosto inefficiente. Una minore quantità di luce in ingresso aumenta l'efficienza ma influisce negativamente sulle prestazioni della rete neurale. Ma c'è un "punto debole, "Bernstein dice, che utilizza la minima potenza ottica mantenendo la precisione.

Quel punto debole per gli acceleratori di intelligenza artificiale viene misurato in quanti joule sono necessari per eseguire una singola operazione di moltiplicazione di due numeri, ad esempio durante la moltiplicazione di matrici. Proprio adesso, gli acceleratori tradizionali si misurano in picojoule, o un trilionesimo di joule. Gli acceleratori fotonici misurano in attojoule, che è un milione di volte più efficiente.

Nelle loro simulazioni, i ricercatori hanno scoperto che il loro acceleratore fotonico potrebbe funzionare con un'efficienza sub-attojoule. "C'è una potenza ottica minima che puoi inviare, prima di perdere la precisione. Il limite fondamentale del nostro chip è molto più basso degli acceleratori tradizionali… e più basso di altri acceleratori fotonici, "dice Bernstein.

Questa storia è stata ripubblicata per gentile concessione di MIT News (web.mit.edu/newsoffice/), un popolare sito che copre notizie sulla ricerca del MIT, innovazione e didattica.