Un nanofilo di ossido di titanio funge sia da diodo che da memristore

Ricercatori presso AMBER, il centro di scienza dei materiali finanziato dalla Science Foundation Ireland, e la Scuola di Chimica, Trinity College di Dublino, hanno sviluppato una soluzione per aumentare la velocità di interazione tra processore e memoria nei computer e altri dispositivi elettronici.

Invece di ogni cella di memoria che memorizza solo un singolo pezzo o "bit" di informazioni, il team, guidato dal professor John Boland con i ricercatori Curtis O'Kelly e Jessamyn Fairfield, ha sviluppato una memoria multilivello in cui è possibile programmare un numero di bit memorizzati in una singola cella. La memoria multilivello aumenta la velocità di comunicazione riducendo il numero di celle di memoria.

Sia che la tua app preferita funzioni su un telefono cellulare o su un supercomputer, le prestazioni non dipendono più esclusivamente dalla potenza del cervello o dalla cosiddetta velocità del processore. Funzionare, il processore deve comunicare in modo efficiente con la memoria sul chip. Le proprietà dei fili metallici che collegano il processore e la memoria forniscono un limite di velocità fondamentale.

Professor John Boland, AMBRA, ha spiegato:"I processori e la memoria comunicano utilizzando il linguaggio goffo del codice binario. La memoria su chip convenzionale memorizza le informazioni come '1' e '0', che riflette la presenza o l'assenza di carica nella posizione di memoria. Per esempio, 2014 in linguaggio binario richiede 11 celle di memoria. Il computer impiega tempo per accedere a un numero così elevato di celle e quindi le prestazioni complessive sono compromesse. Il nuovo processo riduce il numero di celle necessarie".

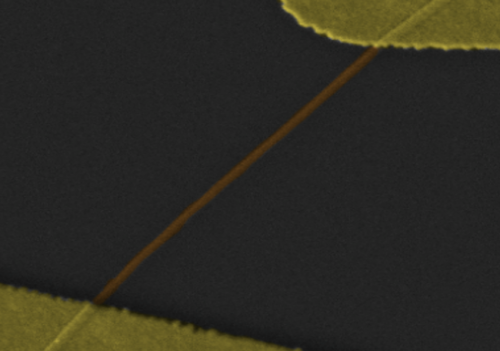

Lo schema proposto dai ricercatori AMBER opera su un principio diverso; la resistenza al flusso di carica, nota come memoria resistiva che alla fine porta a un'elaborazione più snella con meno celle ma ognuna con più livelli di memoria. Un vantaggio particolare del nuovo approccio è che è possibile regolare arbitrariamente il numero di livelli di memoria all'interno di ciascuna cella.

"La scoperta apre una serie di possibilità per il consumatore che porta a piccole, elettronica più economica e veloce. Avendo dimostrato sei livelli di memoria per cella, crediamo che la tecnologia possa essere sviluppata per visualizzare ancora più livelli di memoria per cella. Un linguaggio di memoria con una maggiore densità può aumentare l'efficienza e la velocità della tecnologia desktop e mobile riducendo il numero di posizioni di memoria, ", ha detto il professor Boland.

"Ulteriori ricerche si concentreranno sull'integrazione di questa tecnologia con le capacità di fabbricazione del settore esistenti, in modo che la società possa continuare a raccogliere i benefici con una tecnologia nuova e migliorata, " ha concluso il professor Boland.