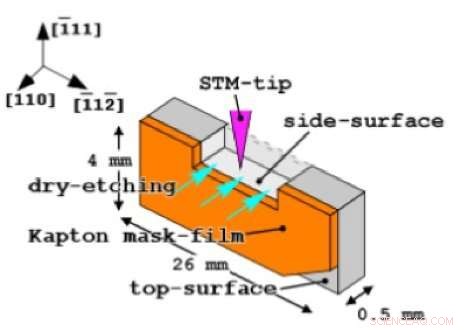

Figura 1. Uno schema di un campione di Si(110) con una maschera a film di Kapton:incisione a secco dalla superficie superiore (110) e punta STM che si avvicina alla superficie laterale (-111). Credito:Università di Osaka

Una collaborazione di ricerca tra l'Università di Osaka e il Nara Institute of Science and Technology per la prima volta ha utilizzato la microscopia a effetto tunnel (STM) per creare immagini di superfici laterali atomicamente piatte di cristalli di silicio 3-D. Questo lavoro aiuta i produttori di semiconduttori a continuare a innovare mentre producono piccoli, Più veloce, e chip per computer più efficienti dal punto di vista energetico per computer e smartphone.

Ciascuno dei nostri computer e smartphone sono caricati con milioni di minuscoli transistor. La velocità di elaborazione di questi dispositivi è aumentata notevolmente nel tempo poiché il numero di transistor che possono essere inseriti in un singolo chip del computer continua ad aumentare. Sulla base della legge di Moore, il numero di transistor per chip raddoppierà circa ogni 2 anni, e in questa zona sembra reggere. Per mantenere questo ritmo di rapida innovazione, i produttori di computer sono continuamente alla ricerca di nuovi metodi per rendere ogni transistor sempre più piccolo.

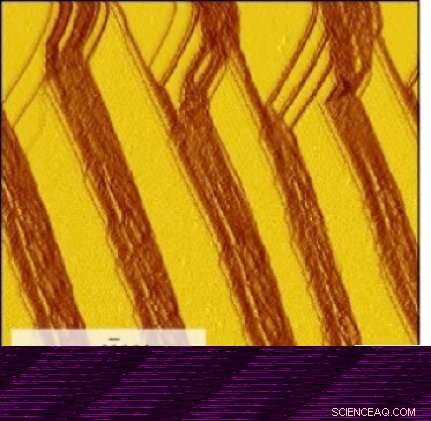

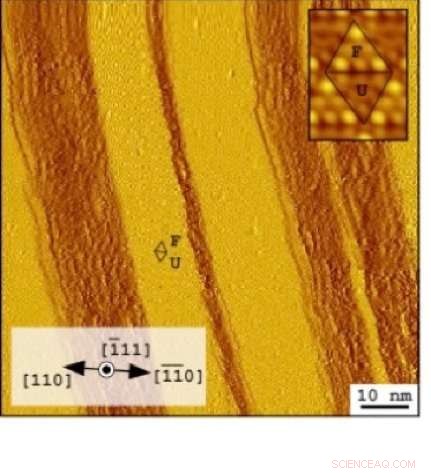

Figura.3. Immagini STM di derivazione spaziale con 200x200 nm^2 a Vs =+1,5 V. Le terrazze piatte diventano più luminose ei bordi più scuri. La direzione verso il basso va da sinistra ((110) superficie superiore) a destra ((-1-10) superficie posteriore). Credito:Università di Osaka

Gli attuali microprocessori sono realizzati aggiungendo modelli di circuiti a wafer di silicio piatti. Un nuovo modo per stipare più transistor nello stesso spazio è fabbricare strutture 3-D. I transistor ad effetto di campo (FET) di tipo aletta sono chiamati così perché hanno strutture di silicio simili a pinne che si estendono nell'aria, dalla superficie del chip. Però, questo nuovo metodo richiede un cristallo di silicio con una superficie superiore e laterale perfettamente piatta, invece della sola superficie superiore, come con i dispositivi attuali. La progettazione della prossima generazione di chip richiederà una nuova conoscenza delle strutture atomiche delle superfici laterali.

Figura.3. Immagini STM di derivazione spaziale con 200x200 nm^2 a Vs =+1,5 V. Le terrazze piatte diventano più luminose ei bordi più scuri. La direzione verso il basso va da sinistra ((110) superficie superiore) a destra ((-1-10) superficie posteriore). Credito:Università di Osaka

Ora, ricercatori dell'Università di Osaka e del Nara Institute of Science and Technology riferiscono di aver utilizzato STM per visualizzare per la prima volta la superficie laterale di un cristallo di silicio. STM è una tecnica potente che consente di vedere le posizioni dei singoli atomi di silicio. Passando una punta acuminata molto vicino al campione, gli elettroni possono saltare attraverso il divario e creare una corrente elettrica. Il microscopio ha monitorato questa corrente, e determinò la posizione degli atomi nel campione.

"Il nostro studio è un primo grande passo verso la valutazione risolta atomicamente di transistor progettati per avere forme 3-D, ", afferma il coautore dello studio Azusa Hattori.

Per rendere le superfici laterali il più lisce possibile, i ricercatori hanno prima trattato i cristalli con un processo chiamato incisione ionica reattiva. Il coautore Hidekazu Tanaka afferma:"La nostra capacità di guardare direttamente le superfici laterali utilizzando STM dimostra che possiamo realizzare strutture 3D artificiali con un ordinamento della superficie atomica quasi perfetto".