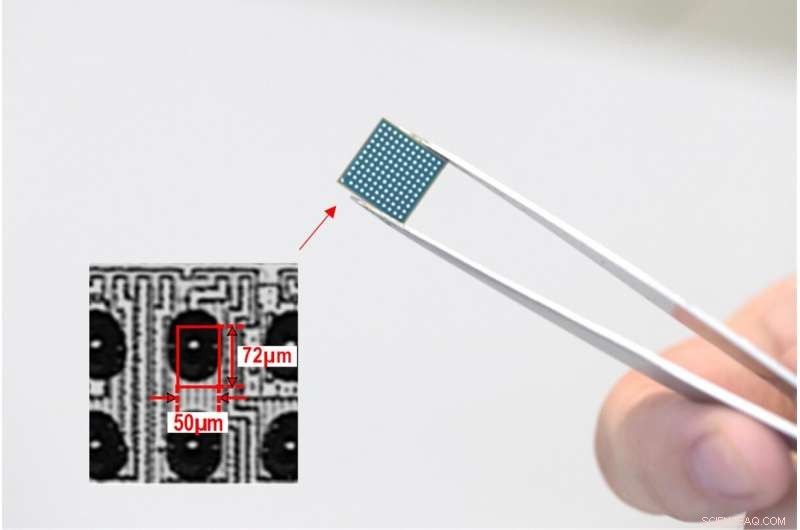

L'intero PLL completamente digitale si inserisce in una regione di 50 × 72 μm2, rendendolo il PLL più piccolo fino ad oggi. Credito:Kenichi Okada

Gli scienziati del Tokyo Institute of Technology (Tokyo Tech) e di Socionext Inc. hanno progettato il più piccolo circuito ad aggancio di fase (PLL) completamente digitale al mondo. I PLL sono circuiti di clock critici praticamente in tutte le applicazioni digitali, e ridurre le loro dimensioni e migliorare le loro prestazioni è un passo necessario per consentire lo sviluppo delle tecnologie di prossima generazione.

Tecnologie nuove o migliorate, come l'intelligenza artificiale, comunicazioni cellulari 5G, e l'Internet delle cose, ci si aspetta che portino cambiamenti rivoluzionari nella società. Ma perché ciò accada, sono indispensabili dispositivi system-on-a-chip (SoC) ad alte prestazioni, un tipo di circuito integrato. Un elemento fondamentale dei dispositivi SoC è il loop ad aggancio di fase (PLL), un circuito che si sincronizza con la frequenza di un'oscillazione di riferimento ed emette un segnale con frequenza uguale o superiore. I PLL generano "segnali di clock, ' le cui oscillazioni fungono da metronomo che fornisce un preciso riferimento temporale per il funzionamento armonioso dei dispositivi digitali.

Per realizzare dispositivi SoC ad alte prestazioni, i processi di fabbricazione per l'elettronica dei semiconduttori devono diventare più sofisticati. Più piccola è l'area per implementare i circuiti digitali, migliori sono le prestazioni del dispositivo. I produttori hanno gareggiato per sviluppare semiconduttori sempre più piccoli. I semiconduttori a 7 nm (un enorme miglioramento rispetto al loro predecessore a 10 nm) sono già in produzione, e si stanno esaminando i metodi per costruirne di 5 nm.

Però, in questo sforzo c'è un grosso collo di bottiglia. I PLL esistenti richiedono componenti analogici, che sono generalmente ingombranti e hanno design difficili da ridimensionare.

Scienziati presso Tokyo Tech e Socionext Inc., guidato dal Prof. Kenichi Okada, hanno affrontato questo problema implementando un PLL a N frazionario "sintetizzato", che richiede solo porte logiche digitali, e nessun componente analogico ingombrante, rendendolo facile da adottare nei circuiti integrati miniaturizzati convenzionali.

Okada e il team hanno utilizzato diverse tecniche per ridurre l'area richiesta, consumo energetico e jitter (fluttuazioni temporali indesiderate durante la trasmissione di segnali digitali) dei loro PLL sintetizzabili. Per diminuire l'area, hanno impiegato un oscillatore ad anello, un oscillatore compatto che può essere facilmente ridimensionato. Per sopprimere il nervosismo, hanno ridotto il rumore di fase - fluttuazioni casuali in un segnale - di questo oscillatore ad anello, utilizzando il "blocco dell'iniezione" - il processo di sincronizzazione di un oscillatore con un segnale esterno la cui frequenza (o multiplo di esso) è vicina a quella dell'oscillatore - su un'ampia gamma di frequenze. Il rumore di fase più basso, a sua volta, ridotto consumo energetico.

Il design di questo PLL sintetizzabile batte quello di tutti gli altri PLL allo stato dell'arte attuali in molti aspetti importanti. Raggiunge le migliori prestazioni di jitter con il minor consumo energetico e l'area più piccola (come si può vedere nella Figura 1). "L'area centrale è 0,0036 mm2, e l'intero PLL è implementato come un unico layout con un singolo alimentatore, " osserva Okada. Inoltre, può essere costruito utilizzando strumenti di progettazione digitale standard, consentendo la sua rapida, a basso sforzo, e produzione a basso costo, rendendolo commercialmente redditizio.

Questo PLL sintetizzabile può essere facilmente integrato nella progettazione di SoC completamente digitali, ed è commercialmente redditizio, rendendolo prezioso per lo sviluppo del tanto ricercato semiconduttore a 5 nm per applicazioni all'avanguardia tra cui l'intelligenza artificiale, internet delle cose e molti altri, dove alte prestazioni e basso consumo energetico sarebbero i requisiti critici. Ma i contributi di questa ricerca vanno oltre queste possibilità. "Il nostro lavoro dimostra il potenziale dei circuiti sintetizzabili. Con la metodologia di progettazione qui impiegata, altri elementi costitutivi dei SoC, come convertitori di dati, circuiti di gestione dell'alimentazione, e ricetrasmettitori wireless, potrebbe anche essere sintetizzato. Ciò aumenterebbe notevolmente la produttività della progettazione e ridurrebbe notevolmente gli sforzi di progettazione, " spiega Okada. Tokyo Tech e Socionext continueranno la loro collaborazione in questo campo per far progredire la miniaturizzazione dei dispositivi elettronici, consentire la realizzazione di tecnologie di nuova generazione.