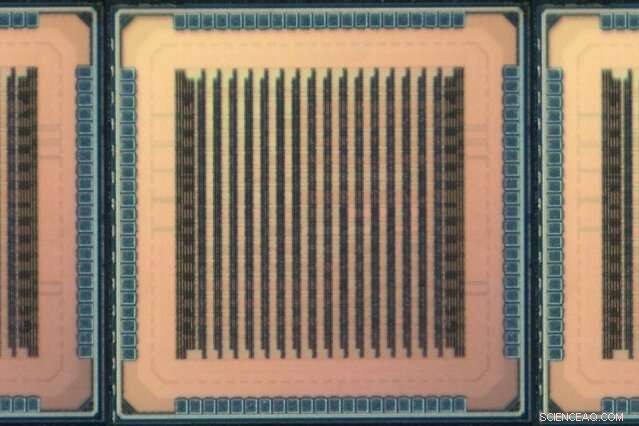

I ricercatori del MIT hanno sviluppato un nuovo chip in grado di calcolare complessi schemi di crittografia a prova di quantistica in modo abbastanza efficiente da proteggere i dispositivi "Internet of Things" (IoT) a bassa potenza. Credito:Massachusetts Institute of Technology

I ricercatori del MIT hanno sviluppato un nuovo circuito di crittografia che può essere utilizzato per proteggere i dispositivi IoT (Internet of Things) a bassa potenza nella prossima era dell'informatica quantistica.

I computer quantistici possono in linea di principio eseguire calcoli che oggi sono praticamente impossibili per i computer classici. Portare i computer quantistici online e sul mercato potrebbe un giorno consentire progressi nella ricerca medica, scoperta di nuovi farmaci, e altre applicazioni. Ma c'è un problema:se gli hacker hanno accesso anche ai computer quantistici, potrebbero potenzialmente violare i potenti schemi di crittografia che attualmente proteggono i dati scambiati tra i dispositivi.

Lo schema di crittografia a resistenza quantistica più promettente di oggi si chiama "crittografia basata su reticolo, " che nasconde informazioni in strutture matematiche estremamente complicate. Ad oggi, nessun algoritmo quantistico conosciuto può sfondare le sue difese. Ma questi schemi sono troppo intensi dal punto di vista computazionale per i dispositivi IoT, che può solo risparmiare energia sufficiente per una semplice elaborazione dei dati.

In un documento presentato alla recente Conferenza internazionale sui circuiti a stato solido, I ricercatori del MIT descrivono una nuova architettura di circuito e trucchi per l'ottimizzazione statistica che possono essere utilizzati per calcolare in modo efficiente la crittografia basata su reticolo. I chip quadrati da 2 millimetri che il team ha sviluppato sono abbastanza efficienti per l'integrazione in qualsiasi dispositivo IoT attuale.

L'architettura è personalizzabile per adattarsi ai molteplici schemi basati su reticolo attualmente in fase di studio in preparazione del giorno in cui i computer quantistici saranno online. "Potrebbe essere tra qualche decennio, ma capire se queste tecniche sono davvero sicure richiede molto tempo, " dice il primo autore Utsav Banerjee, uno studente laureato in ingegneria elettrica e informatica. "Può sembrare presto, ma prima è sempre meglio."

Inoltre, dicono i ricercatori, il circuito è il primo del suo genere a soddisfare gli standard per la crittografia basata su reticolo stabiliti dal National Institute of Standards and Technology (NIST), un'agenzia del Dipartimento del Commercio degli Stati Uniti che trova e scrive regolamenti per gli schemi di crittografia odierni.

Ad unirsi a Banerjee sulla carta c'è Anantha Chandrakasan, decano della School of Engineering del MIT e Vannevar Bush Professor of Electrical Engineering and Computer Science, e Abhishek Pathak dell'Indian Institute of Technology.

Campionamento efficiente

A metà degli anni '90, Il professor Peter Shor del MIT ha sviluppato un algoritmo quantistico che può essenzialmente sfondare tutti i moderni schemi di crittografia. Da allora, Il NIST ha cercato di trovare gli schemi di crittografia postquantistica più sicuri. Questo accade in fasi; ogni fase vaglia una lista degli schemi più sicuri e pratici. Due settimane fa, l'agenzia è entrata nella sua seconda fase per la crittografia postquantistica, con schemi basati su reticolo che costituiscono metà della sua lista.

Nel nuovo studio, i ricercatori hanno prima implementato su microprocessori commerciali diversi schemi di crittografia basati su reticolo NIST dalla prima fase dell'agenzia. Ciò ha rivelato due colli di bottiglia per l'efficienza e le prestazioni:la generazione di numeri casuali e l'archiviazione dei dati.

La generazione di numeri casuali è la parte più importante di tutti gli schemi di crittografia, perché quei numeri vengono utilizzati per generare chiavi di crittografia sicure che non possono essere previste. Questo viene calcolato attraverso un processo in due parti chiamato "campionamento".

Il campionamento prima genera numeri pseudocasuali da un noto, insieme finito di valori che hanno la stessa probabilità di essere selezionati. Quindi, un passaggio di "post-elaborazione" converte quei numeri pseudocasuali in una diversa distribuzione di probabilità con una deviazione standard specificata, un limite per quanto i valori possono variare l'uno dall'altro, che randomizza ulteriormente i numeri. Fondamentalmente, i numeri casuali devono soddisfare parametri statistici scelti con cura. Questo difficile problema matematico consuma circa l'80% di tutta l'energia di calcolo necessaria per la crittografia basata su reticolo.

Dopo aver analizzato tutti i metodi disponibili per il campionamento, i ricercatori hanno scoperto che un metodo, chiamato SHA-3, può generare molti numeri pseudocasuali due o tre volte più efficientemente di tutti gli altri. Hanno ottimizzato SHA-3 per gestire il campionamento crittografico basato su reticolo. In cima a questo, hanno applicato alcuni trucchi matematici per fare un campionamento pseudocasuale, e la conversione post-elaborazione a nuove distribuzioni, più veloce ed efficiente.

Eseguono questa tecnica utilizzando hardware personalizzato ad alta efficienza energetica che occupa solo il 9% della superficie del loro chip. Alla fine, questo rende il processo di campionamento di due ordini di grandezza più efficiente rispetto ai metodi tradizionali.

Dividere i dati

Per quanto riguarda l'hardware, i ricercatori hanno apportato innovazioni nel flusso di dati. La crittografia basata su reticolo elabora i dati in vettori, che sono tabelle di poche centinaia o migliaia di numeri. L'archiviazione e lo spostamento di tali dati richiedono componenti di memoria fisica che occupano circa l'80% dell'area hardware di un circuito.

Tradizionalmente, i dati sono memorizzati su un singolo dispositivo di memoria ad accesso casuale (RAM) a due o quattro porte. I dispositivi multiporta consentono l'elevata velocità di trasmissione dei dati richiesta per gli schemi di crittografia, ma occupano molto spazio.

Per il loro progetto di circuito, i ricercatori hanno modificato una tecnica chiamata "trasformata teorica dei numeri" (NTT), che funziona in modo simile alla tecnica matematica della trasformata di Fourier che scompone un segnale nelle frequenze multiple che lo compongono. L'NTT modificato divide i dati vettoriali e assegna porzioni su quattro dispositivi RAM a porta singola. È ancora possibile accedere a ciascun vettore nella sua interezza per il campionamento come se fosse memorizzato su un singolo dispositivo multiporta. Il vantaggio è che i quattro dispositivi REM a porta singola occupano circa un terzo in meno di un'area totale rispetto a un dispositivo multiporta.

"In pratica abbiamo modificato il modo in cui il vettore è mappato fisicamente nella memoria e modificato il flusso di dati, quindi questa nuova mappatura può essere incorporata nel processo di campionamento. Usando questi trucchi di architettura, abbiamo ridotto il consumo energetico e l'area occupata, mantenendo la produttività desiderata, " dice Banerjee.

Il circuito incorpora anche un piccolo componente di memoria delle istruzioni che può essere programmato con istruzioni personalizzate per gestire diverse tecniche di campionamento, come distribuzioni di probabilità specifiche e deviazioni standard, e diverse dimensioni e operazioni di vettori. Questo è particolarmente utile, poiché gli schemi di crittografia basati su reticolo molto probabilmente cambieranno leggermente nei prossimi anni e decenni.

I parametri regolabili possono essere utilizzati anche per ottimizzare l'efficienza e la sicurezza. Più complesso è il calcolo, minore è l'efficienza, e viceversa. Nella loro carta, i ricercatori spiegano in dettaglio come navigare in questi compromessi con i loro parametri regolabili. Prossimo, i ricercatori hanno in programma di modificare il chip per eseguire tutti gli schemi di crittografia basati su reticolo elencati nella seconda fase del NIST.

Questa storia è stata ripubblicata per gentile concessione di MIT News (web.mit.edu/newsoffice/), un popolare sito che copre notizie sulla ricerca del MIT, innovazione e didattica.