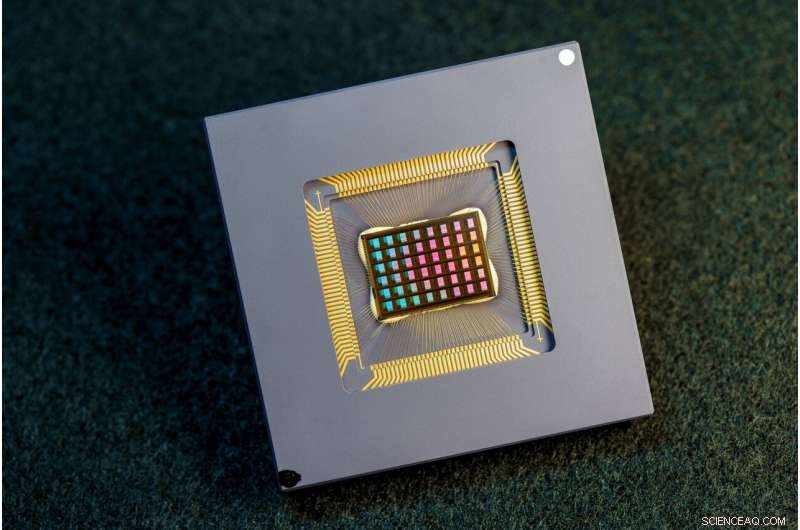

Un team di ricercatori internazionali ha progettato, prodotto e testato il chip NeuRRAM. Credito:David Baillot/Università della California San Diego

Un team internazionale di ricercatori ha progettato e costruito un chip che esegue i calcoli direttamente in memoria e può eseguire un'ampia varietà di applicazioni di intelligenza artificiale, il tutto a una frazione dell'energia consumata dalle piattaforme informatiche per l'elaborazione AI generica.

Il chip neuromorfico NeuRRAM avvicina l'IA all'esecuzione su un'ampia gamma di dispositivi edge, disconnessi dal cloud, dove possono eseguire sofisticate attività cognitive ovunque e in qualsiasi momento senza fare affidamento su una connessione di rete a un server centralizzato. Le applicazioni abbondano in ogni angolo del mondo e in ogni aspetto della nostra vita e spaziano da orologi intelligenti, cuffie VR, auricolari intelligenti, sensori intelligenti nelle fabbriche e rover per l'esplorazione dello spazio.

Il chip NeuRRAM non solo è due volte più efficiente dal punto di vista energetico rispetto ai chip "compute-in-memory" all'avanguardia, una classe innovativa di chip ibridi che esegue calcoli in memoria, ma fornisce anche risultati accurati quanto chip digitali convenzionali. Le piattaforme di intelligenza artificiale convenzionali sono molto più ingombranti e in genere sono vincolate all'utilizzo di server di dati di grandi dimensioni che operano nel cloud.

Inoltre, il chip NeuRRAM è estremamente versatile e supporta molti diversi modelli e architetture di reti neurali. Di conseguenza, il chip può essere utilizzato per molte applicazioni diverse, tra cui il riconoscimento e la ricostruzione delle immagini, nonché il riconoscimento vocale.

"La saggezza convenzionale è che la maggiore efficienza del calcolo in memoria è a scapito della versatilità, ma il nostro chip NeuRRAM ottiene efficienza senza sacrificare la versatilità", ha affermato Weier Wan, il primo autore corrispondente del documento e un recente dottorato di ricerca. laureato alla Stanford University che ha lavorato sul chip mentre era alla UC San Diego, dove è stato co-consulente da Gert Cauwenberghs nel Dipartimento di Bioingegneria.

Il team di ricerca, co-guidato da bioingegneri dell'Università della California a San Diego, presenta i risultati nel numero del 17 agosto di Nature .

Attualmente, l'intelligenza artificiale è sia affamata di energia che computazionalmente costosa. La maggior parte delle applicazioni di intelligenza artificiale sui dispositivi perimetrali comporta lo spostamento dei dati dai dispositivi al cloud, dove l'intelligenza artificiale li elabora e li analizza. Quindi i risultati vengono spostati nuovamente sul dispositivo. Questo perché la maggior parte dei dispositivi edge sono alimentati a batteria e, di conseguenza, hanno solo una quantità limitata di energia che può essere dedicata all'informatica.

Riducendo il consumo energetico necessario per l'inferenza dell'IA all'edge, questo chip NeuRRAM potrebbe portare a dispositivi edge più robusti, più intelligenti e accessibili e a una produzione più intelligente. Potrebbe anche portare a una migliore privacy dei dati poiché il trasferimento di dati dai dispositivi al cloud comporta maggiori rischi per la sicurezza.

Sui chip AI, lo spostamento dei dati dalla memoria alle unità di calcolo è uno dei principali colli di bottiglia.

"E 'l'equivalente di fare un pendolarismo di otto ore per una giornata lavorativa di due ore", ha detto Wan.

Per risolvere questo problema di trasferimento dei dati, i ricercatori hanno utilizzato quella che è nota come memoria resistiva ad accesso casuale, un tipo di memoria non volatile che consente il calcolo direttamente all'interno della memoria anziché in unità di calcolo separate. La RRAM e altre tecnologie di memoria emergenti utilizzate come array di sinapsi per l'elaborazione neuromorfica sono state sperimentate nel laboratorio di Philip Wong, consulente di Wan a Stanford e uno dei principali contributori di questo lavoro. Il calcolo con chip RRAM non è necessariamente nuovo, ma generalmente porta a una diminuzione dell'accuratezza dei calcoli eseguiti sul chip e a una mancanza di flessibilità nell'architettura del chip.

"Il calcolo in memoria è stata una pratica comune nell'ingegneria neuromorfica da quando è stato introdotto più di 30 anni fa", ha affermato Cauwenberghs. "La novità di NeuRRAM è che l'estrema efficienza ora si unisce a una grande flessibilità per diverse applicazioni di intelligenza artificiale senza quasi nessuna perdita di precisione rispetto alle piattaforme di calcolo digitali standard per uso generale."

Una metodologia accuratamente realizzata è stata la chiave del lavoro con più livelli di "co-ottimizzazione" attraverso i livelli di astrazione di hardware e software, dalla progettazione del chip alla sua configurazione per eseguire varie attività di intelligenza artificiale. Inoltre, il team si è assicurato di tenere conto di vari vincoli che vanno dalla fisica dei dispositivi di memoria ai circuiti e all'architettura di rete.

"Questo chip ora ci fornisce una piattaforma per affrontare questi problemi attraverso lo stack, dai dispositivi e circuiti agli algoritmi", ha affermato Siddharth Joshi, assistente professore di informatica e ingegneria all'Università di Notre Dame, che ha iniziato a lavorare al progetto come un dottorato di ricerca studente e ricercatore post-dottorato nel laboratorio Cauwenberghs presso la UC San Diego.

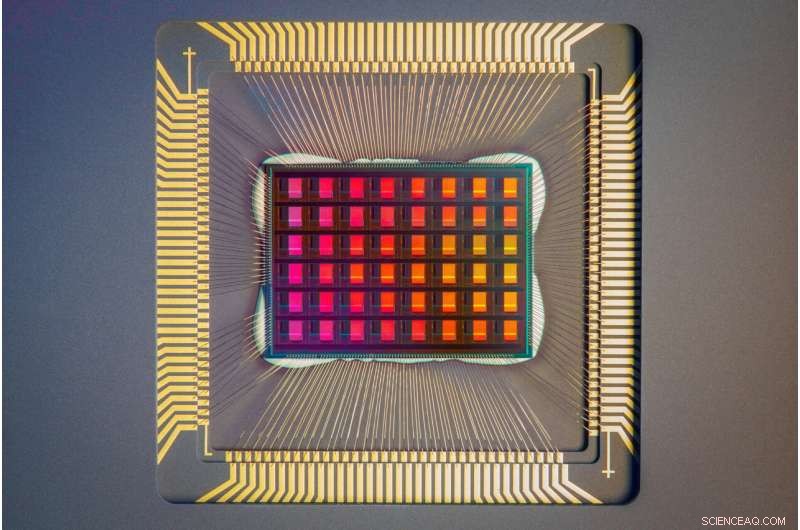

Un primo piano del chip NeuRRAM. Credito:David Baillot/Università della California San Diego

Prestazioni del chip

I ricercatori hanno misurato l'efficienza energetica del chip con una misura nota come prodotto a ritardo di energia o EDP. EDP combina sia la quantità di energia consumata per ogni operazione che il tempo necessario per completare l'operazione. Con questa misura, il chip NeuRRAM raggiunge un EDP da 1,6 a 2,3 volte inferiore (più basso è migliore) e una densità di calcolo da 7 a 13 volte superiore rispetto ai chip all'avanguardia.

I ricercatori hanno eseguito varie attività di intelligenza artificiale sul chip. Ha raggiunto una precisione del 99% su un'attività di riconoscimento delle cifre scritte a mano; 85,7% su un'attività di classificazione delle immagini; e l'84,7% su un'attività di riconoscimento dei comandi vocali di Google. Inoltre, il chip ha anche ottenuto una riduzione del 70% dell'errore di ricostruzione dell'immagine durante un'attività di ripristino dell'immagine. Questi risultati sono paragonabili ai chip digitali esistenti che eseguono calcoli con la stessa precisione di bit, ma con un drastico risparmio di energia.

Researchers point out that one key contribution of the paper is that all the results featured are obtained directly on the hardware. In many previous works of compute-in-memory chips, AI benchmark results were often obtained partially by software simulation.

Next steps include improving architectures and circuits and scaling the design to more advanced technology nodes. Researchers also plan to tackle other applications, such as spiking neural networks.

"We can do better at the device level, improve circuit design to implement additional features and address diverse applications with our dynamic NeuRRAM platform," said Rajkumar Kubendran, an assistant professor for the University of Pittsburgh, who started work on the project while a Ph.D. student in Cauwenberghs' research group at UC San Diego.

In addition, Wan is a founding member of a startup that works on productizing the compute-in-memory technology. "As a researcher and an engineer, my ambition is to bring research innovations from labs into practical use," Wan said.

New architecture

The key to NeuRRAM's energy efficiency is an innovative method to sense output in memory. Conventional approaches use voltage as input and measure current as the result. But this leads to the need for more complex and more power hungry circuits. In NeuRRAM, the team engineered a neuron circuit that senses voltage and performs analog-to-digital conversion in an energy efficient manner. This voltage-mode sensing can activate all the rows and all the columns of an RRAM array in a single computing cycle, allowing higher parallelism.

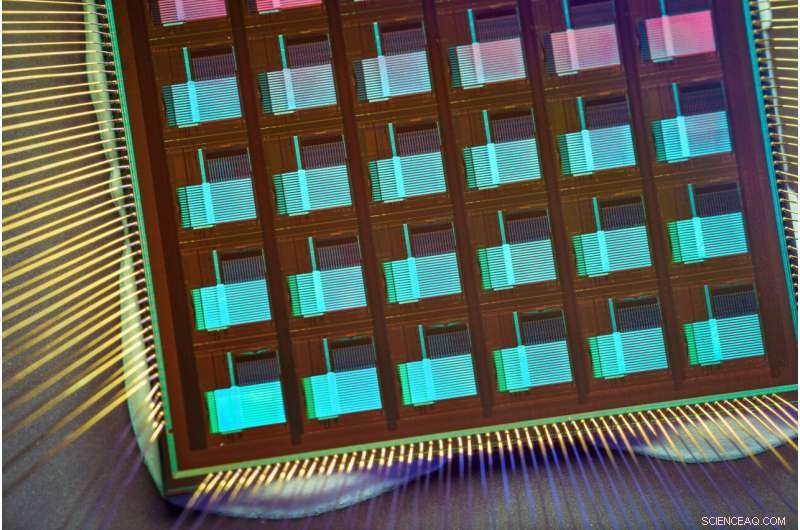

In the NeuRRAM architecture, CMOS neuron circuits are physically interleaved with RRAM weights. It differs from conventional designs where CMOS circuits are typically on the peripheral of RRAM weights.The neuron's connections with the RRAM array can be configured to serve as either input or output of the neuron. This allows neural network inference in various data flow directions without incurring overheads in area or power consumption. This in turn makes the architecture easier to reconfigure.

To make sure that accuracy of the AI computations can be preserved across various neural network architectures, researchers developed a set of hardware algorithm co-optimization techniques. The techniques were verified on various neural networks including convolutional neural networks, long short-term memory, and restricted Boltzmann machines.

As a neuromorphic AI chip, NeuroRRAM performs parallel distributed processing across 48 neurosynaptic cores. To simultaneously achieve high versatility and high efficiency, NeuRRAM supports data-parallelism by mapping a layer in the neural network model onto multiple cores for parallel inference on multiple data. Also, NeuRRAM offers model-parallelism by mapping different layers of a model onto different cores and performing inference in a pipelined fashion.

The NeuRRAM chip uses an innovative architecture that has been co-optimized across the stack. Credit:David Baillot/University of California San Diego

An international research team

The work is the result of an international team of researchers.

The UC San Diego team designed the CMOS circuits that implement the neural functions interfacing with the RRAM arrays to support the synaptic functions in the chip's architecture, for high efficiency and versatility. Wan, working closely with the entire team, implemented the design; characterized the chip; trained the AI models; and executed the experiments. Wan also developed a software toolchain that maps AI applications onto the chip.

The RRAM synapse array and its operating conditions were extensively characterized and optimized at Stanford University.

The RRAM array was fabricated and integrated onto CMOS at Tsinghua University.

The Team at Notre Dame contributed to both the design and architecture of the chip and the subsequent machine learning model design and training. + Esplora ulteriormente