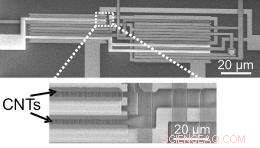

Un'immagine al microscopio elettronico che mostra transistor a nanotubi di carbonio (CNT) disposti in un circuito logico integrato.

(PhysOrg.com) -- Gli ingegneri di Stanford hanno costruito quello che credono sia un chip con gli elementi di elaborazione e archiviazione più avanzati realizzati con nanotubi di carbonio fino ad oggi, escogitando un modo per sradicare la complicazione ostinata dei nanotubi che causano cortocircuiti.

nanotubi, che assomigliano a microscopiche cannucce di filo di pollo arrotolato, sono ampiamente considerati come la potenziale prossima generazione di materiali per consentire una maggiore velocità ed efficienza energetica dei chip dei computer.

I ricercatori hanno presentato oggi i loro risultati all'International Electron Devices Meeting (IEDM) a Baltimora, insieme a un altro progresso nell'uso dei nanotubi per realizzare multistrato, circuiti tridimensionali.

"Questo corpus di lavoro illustra che la tecnologia dei transistor a nanotubi di carbonio è andata oltre il regno della scoperta scientifica e della ricerca ingegneristica, " ha detto H.-S. Philip Wong, un professore di ingegneria elettrica a Stanford e coautore dell'articolo. "Ora siamo in grado di costruire dispositivi e circuiti su scala wafer rispetto alle precedenti dimostrazioni di tipo 'unico nel suo genere'. I dispositivi si trovano in un ambiente circuitale rilevante per le esigenze di sistema sia di oggi che di domani".

La manciata di transistor a nanotubi nei circuiti fabbricati dal team non può essere paragonata alle centinaia di milioni di transistor su un microprocessore commerciale o un chip di memoria, ma la loro disposizione, il modo in cui sono stati realizzati e le loro proprietà sono molto più vicini al livello commerciale rispetto a qualsiasi dispositivo a nanotubi realizzato prima, disse Subhasish Mitra, un assistente professore di informatica e ingegneria elettrica a Stanford.

I transistor sono raggruppati nelle stesse sequenze "a cascata" necessarie per produrre logica computazionale e memoria, e il processo utilizzato per realizzarli è compatibile con lo standard di produzione industriale VLSI (very large scale integration).

"Siamo molto soddisfatti dei rapidi progressi compiuti dai professori Wong e Mitra e dai loro team di ricerca nello sviluppo di queste tecnologie per aiutare a superare gli ostacoli all'ulteriore integrazione di complessi circuiti elettronici a base di carbonio, che porterà a prodotti più utili per le generazioni future, " disse Betsy Weitzman, vicepresidente esecutivo e direttore del Focus Center Research Program della Semiconductor Research Corporation, che ha contribuito a finanziare la ricerca, insieme alla National Science Foundation.

I chip impiegano tre tecniche avanzate inventate a Stanford per superare i problemi endemici associati ai nanotubi. Uno, inventato nel 2007, consente ai transistor di funzionare indipendentemente dal fatto che i nanotubi dei componenti siano perfettamente dritti. Un altro, inventato nel 2008, consente la fabbricazione su scala VLSI di transistor a nanotubi su un chip. Quello annunciato oggi allo IEDM, è un processo per rimuovere in modo affidabile i nanotubi che conducono sempre corrente elettrica anche quando non dovrebbero. Questi fastidiosi nanotubi "metallici" possono cortocircuitare i transistor se non vengono rimossi. La difficoltà che i ricercatori hanno dovuto affrontare è trovare modi per rimuovere tutti i fastidiosi nanotubi, senza danneggiare altre parti di un circuito, compresi i nanotubi che si comportano correttamente.

La nuova tecnica, che i ricercatori chiamano Metallic Nanotube Removal (VMR) compatibile con VLSI, si basa su un'idea proposta per la prima volta da Paul Collins e dai colleghi dell'IBM nel 2001. L'idea era di rompere i nanotubi esponendoli a correnti elevate. Il team di Stanford ha ora reso pratica l'idea su scala VLSI creando una griglia di elettrodi che eliminano i nanotubi indesiderati. La stessa griglia di elettrodi può quindi essere incisa per produrre qualsiasi progetto di circuito, compresi quelli che fanno uso delle tecniche sviluppate da Stanford sopra menzionate.

L'autore principale del documento VMR presentato all'IEDM è lo studente laureato di Stanford in ingegneria elettrica Nishant Patil. Altri autori includono gli studenti laureati in ingegneria elettrica Albert Lin, Jie Zhang e Hai Wei, e lo studente universitario Kyle Anderson.

Circuiti di nanotubi 3D

Cinque membri della squadra (Wei, Patti, Lin, Wong e Mitra) hanno immediatamente seguito l'articolo VMR all'IEDM con un'altra presentazione che descriveva il primo circuito integrato tridimensionale di nanotubi di carbonio multistrato.

Come parcheggi multipiano, i circuiti tridimensionali consentono l'imballaggio di più unità - in questo caso, transistor - in un'area ristretta. sulle patatine, la terza dimensione può anche ridurre le lunghezze di alcuni fili di interconnessione, riduzione dell'energia necessaria per la trasmissione dei dati. Mentre gli ingegneri hanno recentemente iniziato a fare progressi nella costruzione di circuiti tridimensionali impilando e collegando strati realizzati con materiali convenzionali, il lavoro di Stanford mostra che può essere fatto con i nanotubi in un modo che è integrato fin dall'inizio come un design 3-D, ottenendo una maggiore densità di connessioni tra gli strati.

Indicando che i progressi possono essere possibili con i nanotubi, i ricercatori di Stanford sono stati in grado di modellare un prototipo di chip a tre strati con dozzine di transistor a nanotubi collegati in porte logiche funzionanti da nanotubi e cablaggio metallico. Cosa ha reso possibile l'impresa, Mitra ha detto, era l'uso di un processo a temperatura relativamente bassa che i ricercatori hanno sviluppato l'anno scorso in cui i nanotubi vengono trasferiti da un wafer di quarzo su un chip di silicio.

Una sfida rimanente è aumentare il numero di nanotubi che possono essere adeguatamente modellati su una data area di un chip, per consentire di realizzare i milioni di transistor richiesti dai progetti moderni. Non è un ostacolo che i ricercatori si aspettano di non superare.

Entrambi i progetti sono stati supportati dal programma di ricerca Focus Center e dalla Direzione per l'informatica e la scienza e l'ingegneria della National Science Foundation (CISE).

"NSF e in particolare CISE, è molto interessato ad esplorare nuove entusiasmanti vie per ottenere continui miglioramenti delle prestazioni hardware oltre i limiti della legge di Moore, " disse Sampath Kannan, un direttore della divisione CISE presso la National Science Foundation.

"Il team guidato dai professori Mitra e Wong, sostenuto da diverse sovvenzioni del CISE, è una ricerca pionieristica lungo una di queste strade. I loro nuovi risultati sulla tecnica su scala VLSI per trattare i nanotubi di carbonio metallici per la progettazione di circuiti e la loro dimostrazione sperimentale di circuiti CNT compatibili con VLSI immuni alle imperfezioni ci avvicinano alla realizzazione di circuiti integrati che utilizzano nanotubi di carbonio una realtà pratica.

Fornito dalla Stanford University (notizie:web)