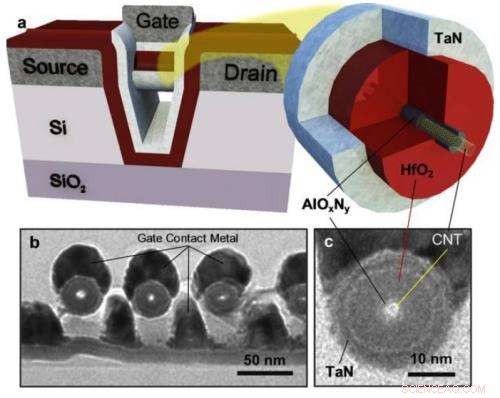

(a) Diagramma in sezione trasversale del CNTFET che illustra come il canale CNT (schema in sezione mostrato a destra) è sospeso attraverso la trincea di silicio e contattato su entrambi i lati dalla sorgente/drenaggio. (b) e (c) mostrano immagini TEM in sezione trasversale di nanotubi con una geometria gate-all-around, che protegge i nanotubi dall'influenza dei dispositivi vicini e dalle cariche vaganti. Credito:Franklin, et al. ©2013 American Chemical Society

(Phys.org) —Durante gli anni '70, anni '80 e '90, le prestazioni dei transistor sono continuamente aumentate secondo alcune semplici regole di scala. Queste regole postulano che le dimensioni del transistor e la tensione di alimentazione dovrebbero diminuire man mano che la densità di potenza rimane costante, con conseguente aumento complessivo delle prestazioni. Però, limitazioni fisiche hanno interrotto il ridimensionamento della tensione di alimentazione nei primi anni 2000, quindi le semplici regole di ridimensionamento non si applicano più. Ora qualsiasi aumento delle prestazioni ha il costo di un aumento del consumo di energia, in modo che le prestazioni dei transistor si siano stabilizzate dalla metà degli anni 2000.

Ora in un nuovo studio, ricercatori dell'IBM T.J. Watson Research Center a Yorktown Heights, New York, hanno sfruttato il potenziale dei nanotubi di carbonio come un modo per estendere le regole di scalabilità e ottenere ulteriori miglioramenti delle prestazioni nei transistor. Un giorno, i transistor realizzati con nanotubi di carbonio possono costituire la spina dorsale di molti dei nostri dispositivi elettronici, compresi smartphone e tablet.

L'interruzione del ridimensionamento che i transistor hanno incontrato nell'ultimo decennio è stata in gran parte dovuta alle caratteristiche fisiche dei transistor stessi, che sono transistor ad effetto di campo (MOSFET) a silicio metallo-ossido-semiconduttore. Negli ultimi anni, i ricercatori hanno studiato la possibilità di sostituire i MOSFET con transistor ad effetto di campo a nanotubi di carbonio (CNTFET). Questi transistor hanno già dimostrato molte caratteristiche interessanti, comprese buone prestazioni a basse tensioni con componenti di canale di lunghezza inferiore a 10 nm, una scala che i MOSFET al silicio non possono raggiungere fisicamente con buone prestazioni.

"Ci sono due ragioni principali per cui i CNTFET forniscono vantaggi che i MOSFET non possono:1) I CNT sono semiconduttori a corpo ultrasottile (~ 1 nm), che consente loro di essere integrati in dispositivi scalati in modo aggressivo senza perdere il controllo sulla corrente nel canale; e 2) i CNTFET possono funzionare a basse tensioni di alimentazione, il che significa che possono fornire il livello di corrente elettrica necessario per pilotare circuiti integrati a una tensione inferiore a quella che i MOSFET potranno mai raggiungere, " ha detto il coautore e ricercatore IBM Aaron D. Franklin Phys.org . "Per quasi un decennio, c'è stata poca o nessuna riduzione della tensione di alimentazione per le tecnologie MOSFET:i CNTFET sono una delle migliori opzioni per cambiare questa tendenza."

Però, per competere con i MOSFET, I CNTFET richiedono ancora diversi importanti progressi, compreso un gate scalabile che può auto-allinearsi ai contatti di source e drain, dispositivi complementari di tipo n e p (che differiscono per la polarizzazione), e compatibilità con l'elaborazione del filo necessaria per costruire circuiti.

Nella loro carta, i ricercatori hanno soddisfatto tutti e tre questi requisiti costruendo un transistor CNT con un gate che circonda completamente il canale CNT. I ricercatori spiegano che questa geometria gate-all-around (GAA) è ideale perché protegge il CNT dall'accoppiamento con i CNT vicini e da cariche vaganti che si avvicinano troppo su una scala così piccola e causano instabilità.

"Il più grande significato di questo lavoro è l'implementazione di un cancello che avvolge completamente i canali CNT cilindrici, "Ha detto Franklin. "Poiché i nanotubi sono solo singole molecole di ~ 1 nm di diametro e sono costituiti da un singolo guscio di atomi (cavo all'interno), sono molto sensibili alle perturbazioni elettriche nelle loro vicinanze. Avvolgendo ogni canale CNT nel proprio gate dielettrico e metallico, si isolano da tali perturbazioni e avvicinano i dispositivi a una tecnologia riproducibile e affidabile".

Il gate avvolgente è anche autoallineato con i contatti di source e drain senza richiedere litografia. Come un cancello autoallineato, non si sovrappone o si sovrappone alla sorgente/scarico, ma si adatta quasi perfettamente, che è importante per garantire un buon percorso per il flusso di carica. I ricercatori potrebbero anche ridurre la lunghezza del gate fino a 20 nm, e prevedere che è possibile un ulteriore ridimensionamento per canali CNT ancora più piccoli.

Il gate può essere utilizzato anche per realizzare dispositivi di tipo n e p utilizzando diversi materiali dielettrici per cambiare la polarità. Sebbene il dispositivo di tipo n abbia prestazioni migliori rispetto al dispositivo di tipo p, i ricercatori prevedono che quest'ultimo potrebbe essere migliorato creando regioni spaziali più sottili, poiché questi distanziatori creano una barriera per caricare il trasporto.

I ricercatori hanno anche eseguito simulazioni quantistiche del CNTFET per confermare la loro comprensione del funzionamento del dispositivo. I risultati della simulazione corrispondevano strettamente ai risultati sperimentali, e ha anche permesso ai ricercatori di proiettare l'impatto di diverse variabili sulle prestazioni del dispositivo, compreso lo spessore del distanziatore e il drogaggio. Queste modifiche potrebbero teoricamente aumentare la corrente, diminuire la corrente, e fornire uno swing sottosoglia molto vicino al limite teorico di 60 mv/dec, il che significa che il transistor può passare molto rapidamente tra gli stati on e off.

Andando avanti, i risultati dimostrano che gli array di CNT possono essere integrati in scalabili, transistor di tipo n e p autoallineati con porte avvolgenti ideali. I ricercatori prevedono che, con ulteriore ottimizzazione, questi CNTFET potrebbero un giorno fungere da bassa tensione, transistor ad alte prestazioni che hanno un impatto diffuso sulle applicazioni future.

"In IBM, abbiamo dimostrato negli ultimi anni che è possibile ottenere eccellenti prestazioni CNTFET fino a lunghezze di canale inferiori a 10 nm e ora è possibile farlo in una struttura wrap-gate tecnologicamente compatibile, " Franklin ha detto. "La sfida più grande rimanente a livello di dispositivo è migliorare l'iniezione di vettori nei contatti metallo-CNT dei dispositivi. Quando i contatti vengono ridimensionati alle piccole dimensioni necessarie per una tecnologia, la resistenza di contatto aumenta notevolmente e deve essere affrontata. Sebbene questo problema non sia esclusivo dei CNTFET (i MOSFET di tutti i tipi soffrono allo stesso modo), è un ostacolo che richiede una risoluzione per poter accedere al pieno potenziale di una tecnologia CNT.

"Fuori dall'area del dispositivo, i due principali ostacoli materiali sono continuare ad aumentare la purezza e l'isolamento dei CNT semiconduttori dalle loro controparti metalliche e assemblare con precisione i CNT in posizioni precise su un substrato. Entrambe queste aree hanno visto progressi impressionanti nell'ultimo anno, sia da IBM che da altri gruppi di ricerca."

© 2013 Phys.org. Tutti i diritti riservati.