L'architettura generale di un MOSFET tradizionale rispetto a un FET 2D. Un FET (transistor ad effetto di campo) è un dispositivo per regolare il flusso di portatori di carica (come gli elettroni) attraverso un canale con tre terminali:una sorgente, un drenaggio e un gate. Un MOSFET (transistor a effetto di campo a semiconduttore a ossido di metallo) è di gran lunga il tipo di FET più utilizzato ed è un elemento costitutivo dell'elettronica moderna, utilizzato nei dispositivi elettronici commerciali da oltre 50 anni. Una delle principali differenze tra il MOSFET 3D tradizionale e la "tecnologia emergente" del FET 2D è che il canale in un MOSFET tradizionale è in un materiale 3D, mentre il canale di un FET 2D è un materiale 2D. Credito:Sean Kelley/NIST

I transistor sono gli elementi costitutivi dell'elettronica moderna, utilizzati in tutto, dai televisori ai laptop. Poiché i transistor sono diventati più piccoli e compatti, così anche l'elettronica, motivo per cui il tuo cellulare è un computer super potente che sta nel palmo della tua mano.

Ma c'è un problema di ridimensionamento:i transistor ora sono così piccoli che è difficile spegnerli. Un elemento chiave del dispositivo è il canale che i portatori di carica (come gli elettroni) viaggiano tra gli elettrodi. Se quel canale diventa troppo corto, gli effetti quantistici consentono agli elettroni di saltare efficacemente da un lato all'altro anche quando non dovrebbero.

Un modo per superare questo ostacolo al dimensionamento consiste nell'utilizzare strati di materiali 2D, che sono spessi solo un singolo atomo, come canale. I canali atomicamente sottili possono aiutare a abilitare transistor ancora più piccoli rendendo più difficile il salto degli elettroni tra gli elettrodi. Un noto esempio di materiale 2D è il grafene, i cui scopritori hanno vinto il Premio Nobel per la fisica nel 2010. Ma ci sono altri materiali 2D, e molti credono che siano il futuro dei transistor, con la promessa di ridurre lo spessore del canale rispetto al suo attuale limite 3D di pochi nanometri (nm, miliardesimi di metro) a uno spessore inferiore a un singolo nanometro.

Sebbene la ricerca sia esplosa in quest'area, un problema è stato costantemente trascurato, secondo un team di scienziati del National Institute of Standards and Technology (NIST), della Purdue University, della Duke University e della North Carolina State University. I materiali 2D e le loro interfacce, che i ricercatori intendono essere piatti quando impilati l'uno sull'altro, potrebbero, infatti, non essere piatti. Questa non planarità a sua volta può influire in modo significativo sulle prestazioni del dispositivo, a volte in modo positivo ea volte in modo negativo.

In un nuovo studio pubblicato nel numero del 26 aprile 2022 di ACS Nano , il team di ricerca riporta i risultati delle misurazioni della planarità di queste interfacce nei dispositivi a transistor che incorporano materiali 2D. Sono il primo gruppo a acquisire immagini di microscopia ad alta risoluzione che mostrano la planarità di questi strati 2D in array di dispositivi completi, su una scala relativamente ampia, circa 12 micrometri (milionesimi di metro) rispetto ai più comuni da 10 nm a 100- nm.

Gli scienziati hanno immaginato con successo una serie di interfacce 2D-2D e 2D-3D nei dispositivi che hanno creato utilizzando una varietà di metodi di fabbricazione comuni. I loro risultati mostrano che presumere che le interfacce siano piatte quando non lo sono è un problema molto più grande di quanto i ricercatori del settore avrebbero potuto realizzare.

"Stiamo illuminando la comunità su un problema che è stato trascurato", ha affermato Curt Richter del NIST. "Sta frenando l'adozione dei nuovi materiali. Il primo passo per risolvere il problema è sapere di avere un problema."

I potenziali vantaggi includono il conferimento alla comunità scientifica di un maggiore controllo sulla fabbricazione dei propri dispositivi.

"La mancanza di comprensione della planarità dell'interfaccia 2D è un ostacolo importante per il miglioramento dei dispositivi basati su materiali 2D", ha affermato l'autore principale Zhihui Cheng, del NIST e della Purdue University al momento della pubblicazione. "Abbiamo messo a punto un metodo per quantificare la planarità rispetto alla risoluzione angstrom. Questo apre molte finestre alle persone per esplorare la tensione e le interazioni alle interfacce 2D."

Non così piatto come pensi

In un transistor tradizionale, un elettrodo sorgente 3D rilascia elettroni attraverso un canale 3D a un elettrodo di drenaggio 3D. Nei transistor 2D, gli elettroni viaggiano attraverso un materiale 2D. Le aree in cui questi diversi materiali si incontrano sono chiamate interfacce.

Una mancanza di planarità su queste interfacce può causare problemi con il flusso di corrente nei dispositivi che utilizzano materiali 2D. Ad esempio, se c'è un intimo contatto fisico tra il metallo sorgente e il canale 2D, allora ci sarà anche un intimo contatto elettrico e la corrente scorrerà senza intoppi. Al contrario, gli spazi tra il materiale del canale 2D e la sorgente compromettono il contatto elettrico, riducendo il flusso di corrente.

Nel loro articolo, i ricercatori esplorano diversi tipi di interfacce 2D, comprese quelle realizzate tra la sorgente di nichel e gli elettrodi di drenaggio, un canale 2D costituito dal disolfuro di molibdeno cristallino 2D (MoS2 ), uno strato incapsulante del nitruro di boro esagonale cristallino (hBN) e ossido di alluminio.

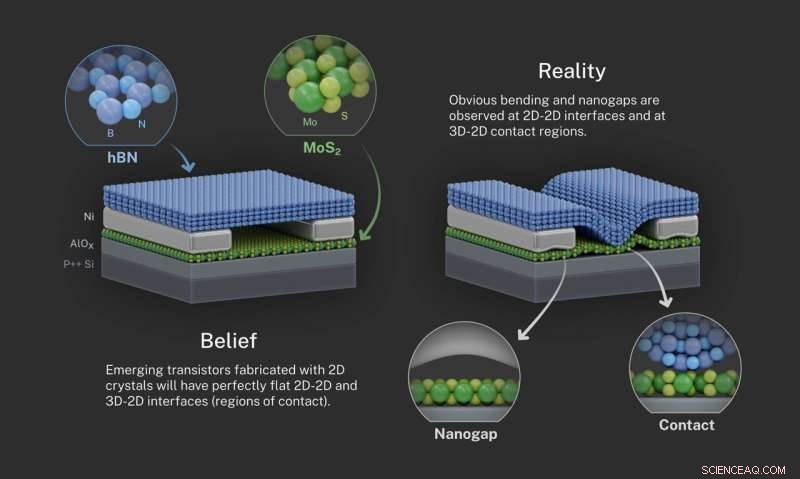

I ricercatori generalmente si aspettano che i transistor fabbricati con cristalli 2D abbiano interfacce 2D-2D e 3D-2D perfettamente piatte (regioni di contatto). Ma nuove prove mostrano che in realtà ci sono evidenti piegamenti e nanogap su queste interfacce. Credito:Sean Kelley/NIST

Gli scienziati in genere mettono i materiali 2D e 3D uno sopra l'altro durante il processo di fabbricazione del dispositivo. Ad esempio, i ricercatori a volte impilano materiali 2D su contatti metallici pre-modellati. Ma il team di ricerca ha scoperto che questo tipo di impilamento di materiali 2D ha avuto un profondo effetto sulla loro planarità, in particolare vicino alla regione di contatto. L'aggiunta di hBN ha causato il MoS2 deformarsi fino a 10 nm su un lato del contatto. Le aree più lontane dai contatti tendevano ad essere relativamente piatte, sebbene alcune di queste aree avessero ancora un divario da 2 a 3 nm.

Durante il test degli effetti della deposizione dello strato atomico (una tecnica comune utilizzata per deporre un sottile strato di materiale) sulla planarità dell'interfaccia 2D, il team di ricerca ha scoperto che un'interfaccia diretta tra ossido di alluminio e MoS2 è più deformato rispetto alle interfacce tra hBN e MoS2 . Durante lo studio della planarità dell'interfaccia di contatto 3D-2D, il team ha scoperto nanocavità sorprendentemente grandi che si formano nell'interfaccia tra i contatti di nichel e il 2D MoS2 canale.

Per collegare queste interfacce non piatte alle preoccupazioni del mondo reale sulle prestazioni del dispositivo, il team ha testato le caratteristiche elettriche di un transistor realizzato con questi materiali. I ricercatori hanno scoperto che la maggiore non planarità nel canale ha avuto l'effetto di migliorare effettivamente le prestazioni del dispositivo.

"Nel complesso, questi risultati rivelano quanto la struttura delle interfacce 2D-2D e 2D-3D dipenda dai materiali e dal processo di fabbricazione", ha affermato Cheng.

Per effettuare le sue osservazioni, il gruppo ha utilizzato un tipo di microscopia elettronica a trasmissione a scansione ad alta risoluzione (scanning TEM), in grado di risolvere le immagini a livello di singoli atomi.

"Gran parte di questo campo è pura ricerca", ha detto Richter. "Le persone produrranno uno o forse due dispositivi e non hanno extra che possono dare a un microscopista per fare a pezzi". In questo studio, invece, il punto era realizzare i dispositivi e poi analizzarli.

"Non abbiamo fatto nulla di super speciale con le misurazioni", ha continuato Richter. "Ma la combinazione del know-how nella misurazione elettrica e dell'esperienza TEM ad alta risoluzione non è una cosa comune."

"Con la risoluzione sub-angstrom e la lunghezza del record nella sezione trasversale TEM, oltre alla correlazione con le caratteristiche del dispositivo, il nostro lavoro ha ampliato e approfondito i punti di vista sulla complessità e la complessità delle interfacce 2D", ha affermato Cheng.

Con vantaggi per tutti

Le applicazioni del lavoro includono la riduzione delle variazioni indesiderate da dispositivo a dispositivo, di cui la planarità 2D è un fattore che contribuisce in modo significativo, hanno affermato i ricercatori.

Il metodo di imaging potrebbe anche in definitiva aiutare a dare agli scienziati un maggiore controllo sulla fabbricazione. Alcuni processi introducono sollecitazioni meccaniche nelle strutture 2D, attorcigliandole come un asciugamano strizzato o schiacciandole e allungandole come una fisarmonica. Ciò può modificare le prestazioni di un dispositivo in modi imprevedibili che gli scienziati non comprendono ancora completamente. Una migliore comprensione di come lo sforzo influisca sulle prestazioni del dispositivo può offrire ai ricercatori un maggiore controllo su queste prestazioni.

"La tensione non è sempre una brutta cosa", ha detto Richter. "I transistor di fascia alta che le persone producono oggi hanno effettivamente una deformazione incorporata per farli funzionare meglio. Con i materiali 2D non è così ovvio come farlo, ma potrebbe essere possibile utilizzare la non planarità per creare la deformazione desiderata ."

Gli autori sperano che il loro lavoro ispiri nuovi sforzi per aumentare la risoluzione delle misurazioni della planarità per le interfacce 2D, anche a una risoluzione inferiore all'angstrom.

"Abbiamo alcuni dati preliminari, ma in realtà è solo l'inizio di questa indagine", ha detto Cheng. + Esplora ulteriormente