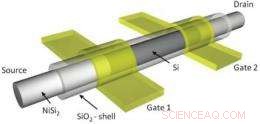

Il nucleo del transistor riconfigurabile è costituito da una struttura a nanocavi incorporata in un guscio di biossido di silicio. Gli elettroni o le lacune fluiscono dalla sorgente a un'estremità del nanofilo attraverso due porte al drenaggio all'altra estremità del nanofilo. Una porta viene utilizzata per programmare la polarità p o n, mentre l'altra porta sintonizza la conduttanza attraverso il nanofilo. Credito immagine:©Namlab gGmbH

(PhysOrg.com) -- La maggior parte dei dispositivi elettronici odierni contiene due diversi tipi di transistor ad effetto di campo (FET):di tipo n (che utilizzano gli elettroni come portatore di carica) e di tipo p (che utilizzano fori). In genere, un transistor può essere solo di un tipo o dell'altro, ma non entrambi. Ora in un nuovo studio, i ricercatori hanno progettato un transistor che può riconfigurarsi come tipo n o tipo p se programmato da un segnale elettrico. Un insieme di questi "transistori universali" può, in linea di principio, eseguire qualsiasi operazione di logica booleana, il che significa che i circuiti potrebbero svolgere lo stesso numero di funzioni logiche con meno transistor. Questo vantaggio potrebbe portare a hardware più compatto e nuovi progetti di circuiti.

I ricercatori che hanno progettato il transistor, guidato da Walter M. Weber presso Namlab gGmbH a Dresda, Germania, hanno pubblicato il nuovo concetto in un recente numero di Nano lettere .

“I nanofili sintetici sono usati per realizzare il proof-of-principio, ” ha detto Weber PhysOrg.com . "Però, il concetto è completamente trasferibile alla tecnologia al silicio CMOS all'avanguardia e può utilizzare processi autoallineati.

Il nucleo del nuovo transistor è costituito da un singolo nanofilo costituito da una struttura metallo-semiconduttore-metallo, che è incorporato in un guscio di biossido di silicio. Gli elettroni o le lacune fluiscono dalla sorgente a un'estremità del nanofilo attraverso due porte al drenaggio all'altra estremità del nanofilo. Le due porte controllano il flusso di elettroni o lacune in modi diversi. Un gate seleziona il tipo di transistor scegliendo di utilizzare elettroni o fori, mentre l'altro gate controlla gli elettroni o le lacune sintonizzando la conduttanza del nanofilo.

L'uso di un gate per selezionare la configurazione di tipo p o n è molto diverso dai transistor convenzionali. Nei transistor convenzionali, l'operazione di tipo p o n deriva dal drogaggio che si verifica durante il processo di fabbricazione, e non può essere modificato una volta realizzato il transistor. In contrasto, il transistor riconfigurabile non utilizza alcun drogaggio. Anziché, una tensione esterna applicata ad una porta può riconfigurare il tipo a transistor anche durante il funzionamento. La tensione fa sì che la giunzione Schottky vicino al gate blocchi il flusso di elettroni o lacune attraverso il dispositivo. Quindi se gli elettroni sono bloccati, i fori possono fluire e il transistor è di tipo p. Applicando una tensione leggermente diversa, la riconfigurazione può essere commutata di nuovo, senza interferire con il flusso.

Gli scienziati spiegano che la chiave per far funzionare questa riconfigurazione è la capacità di sintonizzare separatamente il trasporto elettronico attraverso ciascuna delle due giunzioni (una per porta). Le loro simulazioni hanno mostrato che la corrente è dominata dal tunneling, suggerendo che la geometria del nanofilo gioca un ruolo importante nella capacità di controllo indipendente della giunzione.

Poiché il transistor riconfigurabile può eseguire le funzioni logiche di FET di tipo p e n, un singolo transistor potrebbe sostituire sia un FET di tipo p che n in un circuito, che ridurrebbe notevolmente le dimensioni del circuito senza ridurre la funzionalità. Anche in questa prima fase, il transistor riconfigurabile mostra ottime caratteristiche elettriche, compreso un rapporto on/off record e una corrente di dispersione ridotta rispetto ai FET a nanocavi convenzionali. Nel futuro, i ricercatori hanno in programma di migliorare ulteriormente le prestazioni del transistor.

“Stiamo variando le combinazioni di materiali per migliorare ulteriormente le prestazioni del dispositivo, ” ha detto Weber. "Più avanti, sono in fase di realizzazione i primi circuiti che implementano questi dispositivi. … La sfida più grande sarà quella di incorporare i segnali di gate aggiuntivi nel layout della cella consentendo un'interconnessione flessibile con gli altri transistor”.

Copyright 2011 PhysOrg.com.

Tutti i diritti riservati. Questo materiale non può essere pubblicato, trasmissione, riscritto o ridistribuito in tutto o in parte senza l'espresso permesso scritto di PhysOrg.com.