Al centro dell’avanzamento della tecnologia dei chip semiconduttori c’è una sfida fondamentale:creare componenti elettronici più piccoli ed efficienti. Questa sfida è particolarmente evidente nel campo della litografia, il processo utilizzato per creare modelli complessi su materiali semiconduttori (chiamati wafer) per la produzione di chip.

La litografia utilizza una sorta di modello, chiamato fotomaschera, o semplicemente maschera, per creare modelli su wafer semiconduttori. L'industria è sempre alla ricerca di metodi che migliorino la risoluzione e la producibilità sia delle maschere che dei wafer, che produrranno chip più veloci con una maggiore resa di chip correttamente funzionanti.

Le tecniche di litografia computazionale che migliorano la risoluzione e la fedeltà del modello, come la correzione ottica di prossimità (OPC), hanno fatto passi da gigante nell'affrontare queste sfide modificando i singoli modelli di maschera per migliorare sia la stampa della maschera che quella dei wafer.

La tecnologia di litografia inversa (ILT), un approccio inverso matematicamente rigoroso che determina le forme delle maschere che produrranno i risultati desiderati su wafer, è stata vista come una soluzione promettente a molte delle sfide della litografia per chip avanzati. Dalla sua introduzione, più di dieci anni fa, sono stati condotti numerosi studi che dimostrano che le forme curvilinee delle maschere ILT, in particolare, producono i migliori risultati dei wafer.

Tuttavia, fino a poco tempo fa, i tempi di esecuzione associati a questa tecnica computazionale ne limitavano l'applicazione pratica agli "hotspot" critici sui chip. Nel 2019 è stato proposto un sistema completamente nuovo e appositamente realizzato, che include un approccio esclusivo con accelerazione GPU che emula una singola, gigantesca coppia GPU/CPU in grado di elaborare contemporaneamente un'intera soluzione ILT full-chip. Questo nuovo approccio, progettato sistematicamente per l'ILT e l'accelerazione GPU, ha reso l'ILT full-chip una realtà pratica nella produzione.

Tuttavia, questo approccio si basava sulla scrittura di maschere a raggi multipli, un nuovo importante sviluppo nella scrittura di maschere che è basato sui pixel e quindi è indipendente dalla forma in termini di tempo di scrittura. La domanda che rimaneva era se i vantaggi dell'ILT curvilineo a chip completo potessero essere estesi ai writer di maschere a raggio a forma variabile (VSB) che scrivono forme rettilinee (e talvolta triangolari) anziché pixel e che costituiscono la maggior parte dei writer di maschere in tutto il mondo oggi.

Mentre gli scrittori VSB creano rapidamente forme rettangolari più grandi scrivendo una ripresa rettangolare alla volta, i modelli di maschera complessi possono essere un problema perché l'elevato numero di piccoli rettangoli necessari per crearli richiederebbe troppo tempo per essere scritti.

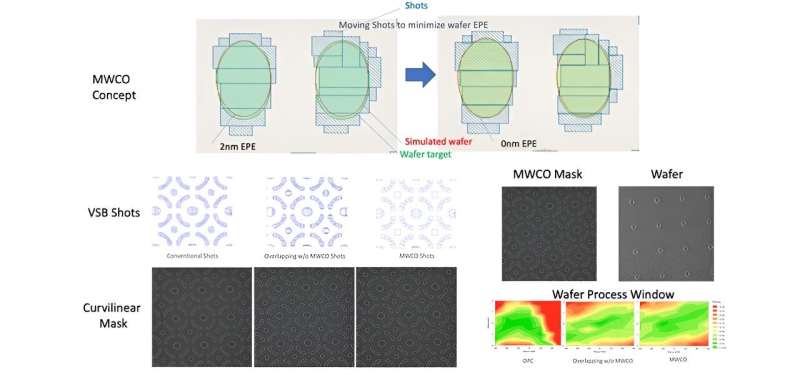

Riportare il proprio lavoro nel Journal of Micro/Nanopatterning, Materials, and Metrology , il team di D2S, Inc. ha inventato un metodo chiamato Mask Wafer Co-Optimization (MWCO) con tre intuizioni:il Mask Writer e lo scanner Wafer sono entrambi filtri passa-basso; gli scatti sovrapposti guidati dalla simulazione maschera/wafer possono creare forme curvilinee con meno scatti; prendendo di mira il modello del wafer, invece del modello della maschera, è possibile creare scatti molto più semplici per stampare il modello del wafer corretto. Utilizzando questa doppia simulazione, la qualità di stampa dei wafer viene ottimizzata in modo iterativo mentre si manipolano i bordi dei colpi VSB per produrre forme rettilinee della maschera target note per essere scrivibili su un scrittore VSB, con un conteggio dei colpi noto e accettabile.

D2S e Micron Technology hanno dimostrato che MWCO può ridurre la variazione del wafer di 3 volte e può migliorare la finestra di processo del wafer di 2 volte rispetto a Micron OPC, indicando un miglioramento sostanziale nella precisione e nell'affidabilità del processo di litografia. Il tempo di scrittura per una maschera ILT completamente curvilinea sarebbe inferiore a 12 ore, soddisfacendo i requisiti di produzione di volumi elevati.

Ciò significa che ora tutti i produttori di semiconduttori possono produrre chip che non solo sono più piccoli ma hanno anche prestazioni più elevate e un consumo energetico inferiore, anche se non hanno accesso a uno scrittore di maschere a raggio multiplo.

Ulteriori informazioni: Linyong (Leo) Pang et al, Rendere possibile l'impossibile:utilizzare scrittori di maschere a fascio di forma variabile e tecnologia di litografia inversa curvilinea a chip completo per contatti/via 193i con co-ottimizzazione maschera-wafer, Journal of Micro/Nanopatterning, Materiali e metrologia (2024). DOI:10.1117/1.JMM.23.1.011207

Fornito da SPIE