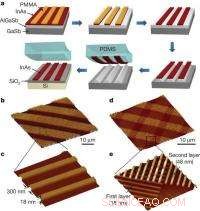

La fabbricazione di un dispositivo all'ossido di indio (InAs) inizia con a) la crescita epitassiale e l'incisione di InAs in array di nanonastri che vengono stampati su un substrato di silicio/silice (Si/SiO2); b) ec) array di nanoribbon InAs su Si/SiO2; d) ed e) sovrastrutture di nanonastri InAs su Si/SiO2. Credito:per gentile concessione di Ali Javey, UC Berkeley

Ci sono buone notizie nella ricerca della prossima generazione di semiconduttori. Ricercatori del Lawrence Berkeley National Laboratory del Dipartimento dell'Energia degli Stati Uniti e dell'Università della California Berkeley, hanno integrato con successo strati ultrasottili dell'arseniuro di indio semiconduttore su un substrato di silicio per creare un transistor su nanoscala con eccellenti proprietà elettroniche. Un membro della famiglia III-V di semiconduttori, l'arseniuro di indio offre numerosi vantaggi come alternativa al silicio, tra cui mobilità e velocità degli elettroni superiori, che lo rende un candidato eccezionale per il futuro a bassa potenza, dispositivi elettronici ad alta velocità.

"Abbiamo mostrato un percorso semplice per l'integrazione eterogenea di strati di arseniuro di indio fino a uno spessore di 10 nanometri su substrati di silicio, "dice Ali Javey, uno scienziato della facoltà nella divisione di scienze dei materiali del Berkeley Lab e un professore di ingegneria elettrica e informatica presso l'UC Berkeley, che ha condotto questa ricerca.

"I dispositivi che abbiamo successivamente fabbricato hanno dimostrato di funzionare vicino ai limiti prestazionali previsti dei dispositivi III-V con una corrente di dispersione minima. I nostri dispositivi hanno anche mostrato prestazioni superiori in termini di densità di corrente e transconduttanza rispetto ai transistor al silicio di dimensioni simili".

Nonostante tutte le sue meravigliose proprietà elettroniche, il silicio presenta limitazioni che hanno spinto a un'intensa ricerca di semiconduttori alternativi da utilizzare nei dispositivi futuri. Javey e il suo gruppo di ricerca si sono concentrati sui semiconduttori composti III-V, che presentano eccellenti proprietà di trasporto degli elettroni. La sfida è stata quella di trovare un modo per collegare questi semiconduttori composti al ben consolidato, tecnologia di elaborazione a basso costo utilizzata per produrre i dispositivi a base di silicio di oggi. Data la grande discrepanza reticolare tra silicio e semiconduttori composti III-V, la crescita etero-epitassiale diretta di III-V su substrati di silicio è impegnativa e complessa, e spesso si traduce in un elevato volume di difetti.

"Abbiamo dimostrato quello che chiamiamo un 'XOI, ' o piattaforma tecnologica composta di semiconduttori su isolanti, che è parallelo all'odierna "SOI, ' o piattaforma silicio su isolante, " dice Javey. "Utilizzando un metodo di trasferimento epitassiale, abbiamo trasferito strati ultrasottili di arseniuro di indio monocristallino su substrati di silicio/silice, quindi dispositivi fabbricati utilizzando tecniche di elaborazione convenzionali al fine di caratterizzare il materiale XOI e le proprietà del dispositivo".

I risultati di questa ricerca sono stati pubblicati sulla rivista Natura, in un documento intitolato, "Semiconduttore composto ultrasottile su strati isolanti per transistor su nanoscala ad alte prestazioni". I co-autori del rapporto con Javey erano Hyunhyub Ko, Kuniharu Takei, Rehan Kapadia, Steven Chuang, Hui Fang, Paolo Leu, Kartik Ganapati, Elena Plis, Ha Sul Kim, Szu-Ying Chen, Morten Madsen, Alessandra Ford, Yu-Lun Chueh, Sanjay Krishna e Sayeef Salahuddin.

Per realizzare le loro piattaforme XOI, Javey e i suoi collaboratori hanno coltivato pellicole sottili di arseniuro di indio a cristallo singolo (da 10 a 100 nanometri di spessore) su un substrato sorgente preliminare, quindi hanno modellato litograficamente le pellicole in matrici ordinate di nanonastri. Dopo essere stato rimosso dal substrato di origine attraverso un attacco umido selettivo di uno strato sacrificale sottostante, gli array di nanonastri sono stati trasferiti al substrato di silicio/silice tramite un processo di stampaggio.

Javey ha attribuito le eccellenti prestazioni elettroniche dei transistor XOI alle piccole dimensioni dello strato "X" attivo e al ruolo critico svolto dal confinamento quantistico, che serviva a mettere a punto la struttura della banda del materiale e le proprietà di trasporto. Sebbene lui e il suo gruppo usassero solo l'arseniuro di indio come semiconduttore composto, la tecnologia dovrebbe facilmente adattarsi anche ad altri semiconduttori composti III/V.

"Sono necessarie ricerche future sulla scalabilità del nostro processo per l'elaborazione di wafer da 8 pollici e 12 pollici, " ha detto Giava.

"Andando avanti crediamo che i substrati XOI possano essere ottenuti attraverso un processo di incollaggio di wafer, ma la nostra tecnica dovrebbe consentire di fabbricare transistor di tipo p e n sullo stesso chip per l'elettronica complementare basata su semiconduttori III-V ottimali.

"Per di più, questo concetto può essere utilizzato per integrare direttamente fotodiodi ad alte prestazioni, laser, e diodi emettitori di luce su substrati di silicio convenzionali. Unicamente, questa tecnica potrebbe consentirci di studiare le proprietà dei materiali di base dei semiconduttori inorganici quando lo spessore viene ridotto a pochi strati atomici".