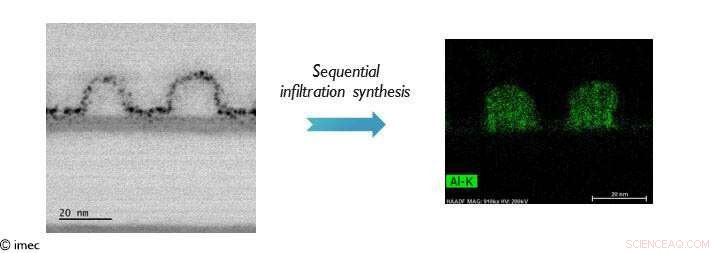

Immagine TEM del modello di fotoresist dopo l'esposizione della litografia (a sinistra) e segnale TEM EDX dall'alluminio per il modello di fotoresist dopo il passaggio SIS (a destra). Credito:IMEC

la sua settimana, alla conferenza SPIE Advanced Lithography 2019, imeco, un polo di ricerca e innovazione leader a livello mondiale nella nanoelettronica e nelle tecnologie digitali, dimostra l'impatto positivo della sintesi di infiltrazione sequenziale (SIS) sul processo di patterning EUVL (litografia ultravioletta estrema). Questa tecnica post-litografia ha dimostrato di ridurre significativamente i nano-guasti stocastici e la rugosità delle linee, contribuendo all'introduzione del modello EUVL dei nodi futuri". Questo lavoro integra i recenti progressi sulla metrologia e sull'incisione, e sugli sviluppi materiali, che sarà presentato in più articoli alla SPIE Advanced Lithography Conference 2019 di questa settimana.

SIS è una tecnica esistente, utilizzato nell'autoassemblaggio diretto (DSA) e ora applicato nella litografia EUV, in cui il fotoresist viene infiltrato con un elemento inorganico per renderlo più duro e robusto, migliorando così le prestazioni di patterning su diversi parametri. Imec e partner mostrano il primo confronto tra un EUVL-SIS e un processo di patterning EUVL standard dimostrando i vantaggi del SIS per quanto riguarda la rugosità, mitigazione del nano-fallimento e variabilità locale. Quando si aggiunge un passaggio SIS durante un trasferimento completo del modello in un livello TiN, imec ha osservato un miglioramento del 60% per l'uniformità della dimensione critica locale (LCDU) intrafield e del 10% per la rugosità del bordo della linea rispetto a un processo di riferimento. Questi miglioramenti del patterning sono proprietà intrinseche di SIS. Anche, il numero di nanorotture – un tipico nano-guasto stocastico – è ridotto di almeno un ordine di grandezza. I risultati sono stati confermati in un caso d'uso industriale rilevante, mostrando una ridotta difettosità in un chip logico con una dimensione critica da punta a punta più piccola del 20% a un LCDU simile a un processo EUVL standard.

Il miglioramento che SIS mostra su tutti i parametri è dovuto all'infrastruttura di litografia e metrologia EUV di imec e ai recenti progressi nel campo del controllo di processo, ricerca sui materiali e sulle incisioni. Il lavoro attuale riunisce questi risultati e competenze in un unico documento, stabilire il SIS come una tecnica significativa di miglioramento del patterning EUV. I progressi su ciascuno degli aspetti integrati e SIS saranno presentati alla conferenza SPIE Advanced Lithography in più articoli.

Il lavoro è stato svolto in collaborazione con ASM e ASML.

"I recenti risultati ottenuti con SIS per la litografia EUV sono stati resi possibili dai progressi che imec e i suoi partner hanno compiuto in vari settori come la scienza dei materiali, deposizione, immagini, e metrologia. Questo è un ottimo esempio di come l'integrazione della conoscenza e gli sforzi combinati di più domini e partner dell'ecosistema consentiranno un percorso per scalare verso N3 e oltre, " ha detto Greg McIntyre, direttore del patterning avanzato presso imec.