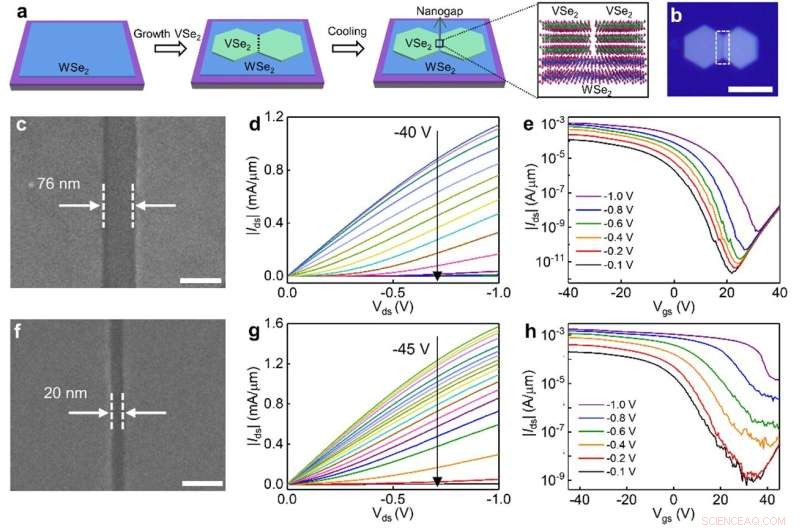

Caratteristiche elettriche dei transistor WSe2 a doppio strato sub-100 nm. a, Illustrazione schematica del flusso di processo per formare transistor WSe2 a doppio strato di lunghezza del canale inferiore a 100 nm con contatti sintetici VSe2 vdW attraverso la formazione di crepe controllate. b, Immagine al microscopio ottico di una coppia di domini esagonali VSe2 sul WSe2 con un apparente nanogap. Barre di scala:5 μm. c, d, immagini SEM dei transistor WSe2 a doppio strato con lunghezze di canale di 76 nm e 20 nm. Barre di scala:100 nm. d, g, Caratteristiche di uscita dei transistor WSe2 da 76 nm e 20 nm a varie tensioni di back-gate con un passo di 5 V. e, h, Curve di trasferimento dei transistor WSe2 a doppio strato da 76 nm e 20 nm a varie tensioni di polarizzazione. Credito:Wu et al.

I semiconduttori 2D potrebbero avere notevoli vantaggi rispetto ai semiconduttori sfusi convenzionali, come il silicio. In particolare, la loro maggiore resistenza agli effetti a canale corto potrebbe renderli particolarmente promettenti per lo sviluppo di transistor ad alte prestazioni, che sono componenti cruciali di tutti i dispositivi elettronici.

I ricercatori dell'Università di Hunan hanno recentemente sviluppato transistor ad alte prestazioni basati sul diseleniuro di tungsteno a doppio strato, un composto inorganico 2D con proprietà semiconduttive. Questi transistor, presentati in un articolo pubblicato su Nature Electronics , è risultato funzionare come i transistor al silicio esistenti con lunghezze di canale e tensioni di pilotaggio simili.

Quando si valutano i transistor basati su semiconduttori 2D, gli ingegneri possono considerare diversi parametri, tra cui la mobilità del vettore e la resistenza di contatto. Questi due valori, tuttavia, sono semplici stime che possono essere calcolate o interpretate erroneamente, risultando in stime incoerenti delle prestazioni di un dispositivo.

La densità di corrente nello stato ON, la quantità di corrente elettrica che scorre attraverso un'area specifica mentre un dispositivo è in funzione, è risultata essere un parametro di valutazione molto più affidabile. Nel loro studio, i ricercatori si sono quindi concentrati in modo specifico sullo sviluppo di un transistor che avesse una densità di corrente nello stato ON paragonabile a quella di dispositivi simili a base di silicio.

"Densità di corrente in stato ON (I acceso ) o la densità di corrente di saturazione è una misura più diretta e affidabile per valutare i transistor con semiconduttori 2D", ha detto a TechXplore Xidong Duan, uno dei ricercatori che hanno condotto lo studio. "Rimane una questione aperta se i transistor 2D possano corrispondere, competere o superare lo stato dell'arte dei transistor al silicio. Rispondere a questa domanda è essenziale per suscitare un interesse più serio da parte della comunità del settore."

La maggior parte dei transistor 2D sviluppati fino ad oggi mostra una I acceso valore significativamente inferiore a quello dei dispositivi al silicio con lunghezze di canale comparabili (L ca ) e bias drain-source (V ds ). Questo alla fine limita il loro potenziale per applicazioni pratiche nel mondo reale.

Nei loro studi precedenti, Duan e i suoi colleghi hanno sintetizzato eterogiunzioni metallo 2D ultrasottili e metallo 2D/semiconduttore cresciute in situ per costruire transistor ad effetto di campo di alta qualità. Inoltre, hanno creato contatti elettrici van der Waals (vdW) privi di danni che potrebbero essere utilizzati per caratterizzare le proprietà intrinseche dei semiconduttori 2D.

"Sebbene i metalli 2D, come i contatti elettrici vdW possano migliorare le prestazioni dei dispositivi a semiconduttori 2D, tali eccellenti proprietà elettriche sono state raggiunte con una lunghezza del canale relativamente lunga, mentre i dispositivi a canale ultracorto con contatto elettrico vdW per valutare le prestazioni dei semiconduttori 2D presentavano ancora sfide ", ha detto Duan. "La fabbricazione di dispositivi a canale ultracorto richiede spesso litografia ad alta risoluzione e processi di metallizzazione aggressivi, che potrebbero introdurre contaminazioni indesiderate o danni ai 2DSC atomicamente sottili, compromettendo così seriamente le loro prestazioni elettroniche."

Basandosi sulle loro scoperte precedenti, Duan e i suoi colleghi hanno utilizzato un processo naturale di formazione di crepe per creare un divario tra le VSe2 unite domini cresciuti su WSe2 a doppio strato . Ciò ha permesso loro di sviluppare WSe2 a doppio strato a canale ultracorto transistor con contatti vdW sintetici ottimizzati, ottenendo un ON record -densità di corrente di stato di 1,72 mA/μm e una resistenza lineare più bassa di 0,50 kΩ·μm a temperatura ambiente.

"I nostri risultati dimostrano per la prima volta che i transistor 2D possono fornire una densità di corrente competitiva a una lunghezza del canale e una tensione di pilotaggio comparabili rispetto ai tradizionali transistor Si", ha affermato Duan. "Ha dato una risposta positiva alla domanda di vecchia data nel campo del "se i transistor 2D possono ottenere prestazioni paragonabili o migliori rispetto ai transistor al silicio".

Finora, la maggior parte degli approcci per la fabbricazione di dispositivi con canali ultracorti prevedeva l'uso di tecniche aggressive, tra cui litografia ad alta risoluzione e processi di metallizzazione. Sebbene queste tecniche possano essere efficaci, introducono anche contaminazioni indesiderate o danneggiano i 2DSC anatomicamente sottili, che possono compromettere seriamente le prestazioni elettroniche dei dispositivi.

Durante la fabbricazione del loro transistor, Duan e i suoi colleghi hanno quindi deciso di adottare un approccio diverso. Più specificamente, hanno utilizzato un contatto vdW pulito e un canale ultracorto, definito dalla formazione di nanocrack controllata dallo stress termico. Ciò ha consentito loro di mantenere il WSe2 il più possibile la struttura e le prestazioni originali del transistor.

"I canali ultracorti ottenuti sono generalmente piuttosto dritti, distinti dagli elettrodi definiti litograficamente che spesso mostrano una rugosità del bordo di linea finita, il che crea una buona condizione per esplorare le prestazioni limite di WSe2 transistor", ha spiegato Duan. "Inoltre, WSe2 a doppio strato i materiali in genere hanno bandgap più piccoli e una migliore immunità ai danni indotti dalla fabbricazione o alla dispersione interfacciale, rispetto alla loro controparte monostrato."

Nelle valutazioni iniziali, i ricercatori hanno osservato notevoli densità di corrente nello stato attivo di 1,0–1,7 mA μm -1 nel doppio strato inferiore a 100 nm WSe2 transistor, superando l'obiettivo di densità di corrente critica per i transistor 2D (ovvero, 1,5 mA μm -1 ). Le loro scoperte potrebbero quindi avere preziose applicazioni nel campo dell'ingegneria elettronica, in quanto dimostrano che i transistor basati su semiconduttori 2D possono fornire densità di corrente competitive a lunghezze di canale e tensioni di pilotaggio paragonabili a quelle dei transistor a base di silicio.

"Riteniamo che la realizzazione della densità di corrente oltre 1,5 mA/mm abbia dato una risposta positiva alla domanda di lunga data nel campo del 'se i transistor 2D possono ottenere prestazioni paragonabili o migliori rispetto ai transistor al silicio'", ha affermato Duan. "Potrebbe ispirare ulteriori sforzi da parte della comunità accademica e industriale per promuovere lo sviluppo di una nuova generazione di semiconduttori 2D e tecnologia di chip dopo i semiconduttori a base di silicio".

In futuro, il recente lavoro di Duan e dei suoi colleghi potrebbe incoraggiare altri team a sviluppare dispositivi simili basati su WSe2 o altri semiconduttori 2D. Tuttavia, i dispositivi che hanno sviluppato finora non sono ancora completamente ottimizzati. Ad esempio, il team è stato costretto a crearli utilizzando dielettrici back-gate relativamente spessi (cioè, 70 nm SiNx ), poiché i dielettrici di alta qualità possono essere difficili da integrare su superfici 2D prive di legami penzolanti. I dielettrici utilizzati hanno una capacità del gate piuttosto piccola, che può limitare l'efficienza di accoppiamento del gate del dispositivo e la misura in cui i gate possono essere controllati.

"I nostri prossimi studi si concentreranno sullo sviluppo di dielettrici di gate di alta qualità con uno spessore minimo di ossido equivalente e uno stato di interfaccia minimo per ottenere un controllo del gate più forte, una corrente più elevata (più vicino agli obiettivi a lungo termine di 3,0 mA μm −1 ), oscillazione sottosoglia minore (più vicino al valore teorico 60 mV/dec) e minore I disattivato (100 pA μm −1 ), rendendo i parametri di prestazione chiave complessivi dei transistor 2D presentano evidenti vantaggi rispetto ai transistor al silicio", ha aggiunto Duan. "Inoltre, prevediamo di migliorare ulteriormente l'integrazione dei transistor 2D per promuovere l'applicazione commerciale dei transistor 2D combinando l'ampia area crescita di semiconduttori 2D TMD e metallo 2D, processo di litografia avanzato per modellare array di contatti metallici 2D e processo di integrazione vdW scalabile." + Esplora ulteriormente

© 2022 Rete Science X