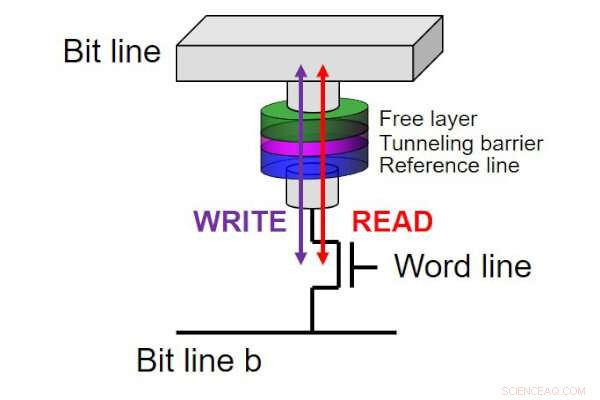

Schema della cella STT-MRAM (Two Terminal Device). Credito:CIES, Università di Tohoku

I ricercatori della Tohoku University hanno annunciato la dimostrazione di una cella di memoria ad accesso casuale magnetoresistivo a coppia spin-orbita (SOT) compatibile con la tecnologia CMOS Si da 300 mm.

La domanda di circuiti integrati (IC) a bassa potenza e ad alte prestazioni è in aumento man mano che i dispositivi di intelligenza artificiale (AI) e Internet-of-Things (IoT) diventano più ampiamente adottati. Con gli attuali circuiti integrati, memorie puramente basate su CMOS come la memoria Flash incorporata (eFlash) e la memoria statica ad accesso casuale (SRAM) sono responsabili di un'elevata percentuale di consumo energetico. Al fine di ridurre il consumo energetico mantenendo alte prestazioni, memorie magnetoresistive ad accesso casuale (MRAM) sono state sviluppate in modo intensivo. Le MRAM di coppia di trasferimento di spin (STT-MRAM) sono le MRAM più sviluppate. Le principali aziende di semiconduttori hanno ora annunciato di essere pronte per la produzione di massa di STT-MRAM per la sostituzione di eFlash.

I ricercatori mirano a sostituire SRAM con MRAM. Per la sostituzione della SRAM, La MRAM deve raggiungere un funzionamento ad alta velocità sopra i 500 MHz. Per soddisfare la domanda, una MRAM alternativa, è stata proposta la cosiddetta MRAM di coppia spin-orbita (SOT-MRAM), che presenta diversi vantaggi per il funzionamento ad alta velocità. A causa di questi vantaggi, È stato sviluppato anche SOT-MRAM; però, la maggior parte degli studi di laboratorio si concentra sui fondamenti dei dispositivi SOT. Per realizzare la sostituzione della SRAM con SOT-MRAM, è necessario dimostrare le elevate prestazioni della cella di memoria SOT-MRAM su un substrato CMOS da 300 mm. Inoltre, è necessario sviluppare il processo di integrazione per SOT-MRAM, per esempio., tolleranza termica contro la ricottura di 400 °C, che è un requisito del processo di back-end di linea CMOS standard.

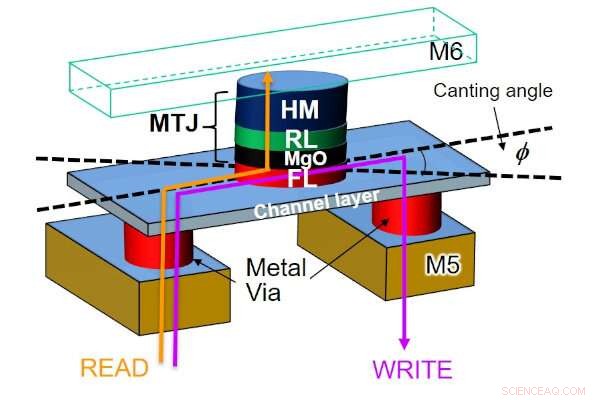

Uno schema della cella SOT-MRAM (dispositivo a tre terminali) Credito:CIES, Università di Tohoku

Una vista schematica della cella SOT-MRAM inclinata. Credito:CIES, Università di Tohoku

Il team di ricerca guidato dai professori Tetsuo Endoh e Hideo Ohno, l'attuale presidente della Tohoku University, ha sviluppato un processo di integrazione per dispositivi SOT compatibili con la tecnologia CMOS da 55 nm e dispositivi SOT fabbricati su substrati CMOS da 300 mm. Il dispositivo SOT di nuova concezione ha raggiunto contemporaneamente una commutazione ad alta velocità fino a 0,35 ns e un fattore di stabilità termica sufficientemente elevato (E/k B T 70) per le applicazioni di memoria non volatile ad alta velocità con robustezza contro la ricottura a 400 °C. Sulla base di questo risultato, il team di ricerca ha integrato il dispositivo SOT con transistor CMOS e infine ha dimostrato il funzionamento ad alta velocità in celle di memoria SOT-MRAM complete.

Questi risultati hanno affrontato i problemi per rendere SOT-MRAM pratico per applicazioni commerciali e quindi offrire un modo per sostituire SRAM con SOT-MRAM, che contribuiranno alla realizzazione di un'elettronica ad alte prestazioni a basso consumo energetico.

I risultati saranno presentati all'IEEE International Electron Devices Meeting 2019 a San Francisco, 7-11 dicembre, 2019.