La globalizzazione della catena di fornitura dei circuiti integrati ha indotto vulnerabilità in varie fasi della produzione dei circuiti integrati. Qui, le fasi delle zone rosse non sono affidabili e possono essere sfruttate da un attaccante. Credito:Rangarajan et al.

Negli ultimi anni, minacce alla sicurezza incentrate sull'hardware sono emerse in diverse fasi della catena di approvvigionamento dei circuiti integrati (IC). Ciò ha consentito la proliferazione di vari attacchi dannosi, come la pirateria sulla proprietà intellettuale (IP), sovrapproduzione illegale di circuiti integrati, e inserimento di Trojan hardware.

Tra tutte le difese esistenti contro la pirateria IP, Finora si è scoperto che solo il blocco logico offre una protezione end-to-end efficace. Per affrontare queste sfide, un team di ricerca presso il New York University Center for Cybersecurity and Quantum Nanoelectronics Lab ha sviluppato un approccio dinamico di mimetizzazione per contrastare il reverse engineering dell'IP in tutte le fasi della catena di approvvigionamento.

"La globalizzazione della filiera dei circuiti integrati ha portato all'esternalizzazione di varie fasi della produzione di chip microelettronici, "Nhil Rangarajan, uno dei ricercatori che ha condotto lo studio, detto TechXplore . "I chip sono generalmente progettati e/o acquistati da un paese, fabbricato in un altro, e infine testato e confezionato altrove. Questa catena mondiale apre molte opportunità agli aggressori di rubare l'IP sottostante, indulgere in sovrapproduzione, o persino inserire modifiche dannose note come Trojan hardware."

Secondo le stime, l'industria dei semiconduttori perde miliardi di dollari ogni anno a causa del furto di proprietà intellettuale. Per mitigare questo danno, la ricerca condotta da Rangarajan e dai suoi colleghi si concentra specificamente sulla prevenzione del furto di proprietà intellettuale.

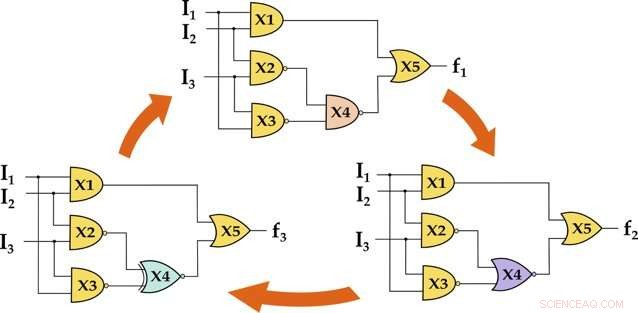

Commutazione dinamica di circuiti polimorfici al volo. Credito:Rangarajan et al.

"L'ispirazione per la nostra idea è venuta dalla natura, dove alcuni animali come il polpo sono in grado di cambiare il loro aspetto fisico per adattarsi al loro ambiente per evitare di essere scoperti da prede o predatori, " ha spiegato Rangarajan. "Abbiamo pensato:perché i circuiti elettronici che cerchiamo di proteggere non possono cambiare anche dinamicamente per evitare il rilevamento da parte di un aggressore?"

I meccanismi di difesa esistenti per la prevenzione del furto di proprietà intellettuale, come il camuffamento statico, richiedere al progettista di fidarsi della fonderia incaricata della fabbricazione del chip. Anzi, il modello di minaccia ideato da Rangarajan e dai suoi colleghi presuppone che un aggressore possa risiedere anche all'interno della fonderia o nella struttura di prova, o potrebbe essere potenzialmente un utente finale.

"Utilizzando proprietà innate come il polimorfismo, multifunzionalità, e la riconfigurabilità post-fabbricazione offerta dai dispositivi spintronici emergenti, come il dispositivo magnetoelectric spin orbit (MESO), siamo stati in grado di ottenere un camuffamento dinamico, "Satwik Patnaik, un altro ricercatore coinvolto nello studio, ha detto a TechXplore. "Il polimorfismo è inteso nei particolari mezzi attraverso i quali il dispositivo può implementare prontamente diverse funzioni booleane in fase di esecuzione, dove la funzionalità è determinata da un meccanismo di controllo interno o esterno."

Nello schema ideato dai ricercatori, una fonderia potenzialmente dannosa fabbrica le porte logiche come "scatole nere, " che può essere configurato solo dal progettista una volta completato il processo di fabbricazione. Ciò impedisce a un utente malintenzionato all'interno della fonderia di decifrare la funzionalità prevista del chip in fase di fabbricazione, in quanto è ancora da configurare.

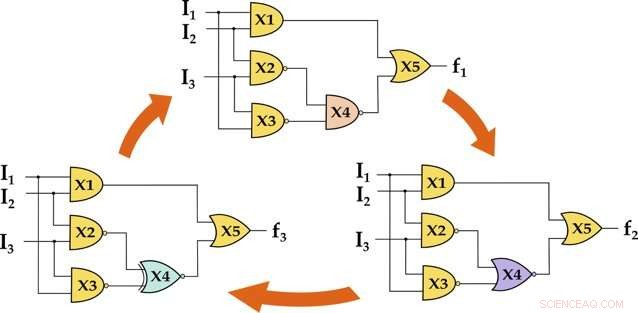

Il camuffamento dinamico è possibile con l'aiuto di nuovi gate spintronici come i gate MESO. Queste porte possono implementare diverse funzionalità booleane in un dispositivo e possono anche passare da una all'altra durante il runtime. Credito:Rangarajan et al.

"Questa proprietà di 'riconfigurabilità post-fabbricazione' consente anche la protezione da strutture di test non affidabili, poiché il chip può essere configurato per qualsiasi funzionalità fittizia sconosciuta a un utente malintenzionato e ripristinato alla funzionalità reale una volta eseguito il test, " ha spiegato Patnaik. "In breve, mentre i lavori precedenti nel camuffamento IC sono statici e devono fidarsi della fonderia, il nostro schema non richiede che il progettista si fidi della fonderia o dell'impianto di prova".

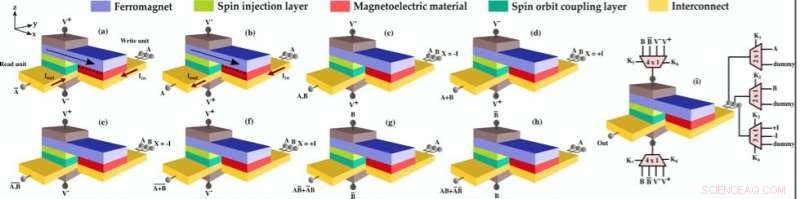

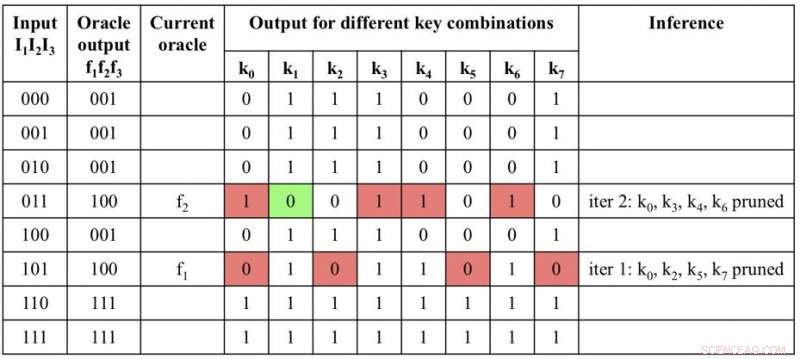

I ricercatori hanno valutato l'efficacia del loro approccio nel contrastare gli attacchi di data mining di test all'avanguardia, come HackTest, e analisi del canale laterale, dove gli avversari mirano a decifrare la funzionalità dell'IP. Hanno anche esplorato le sue prestazioni con potenti attacchi di soddisfacibilità booleana, inclusi SAT e SAT approssimativo (AppSAT), che sono tipicamente preferiti dagli utenti finali.

Il loro approccio di mimetizzazione dinamica ha prodotto risultati promettenti in tutti questi test. Nel futuro, i ricercatori ritengono che potrebbe aiutare a contrastare gli aggressori all'interno di fonderie o strutture di test non affidabili.

"Il nostro schema sfrutta le proprietà uniche dei dispositivi basati su spin, " ha spiegato Rangarajan. "Queste proprietà, soprattutto polimorfismo, non può essere offerto dalle attuali tecnologie CMOS, a causa delle limitazioni fondamentali dei dispositivi CMOS. Vogliamo anche sottolineare che la nozione generale di mimetizzazione dinamica potrebbe essere implementata con altri dispositivi emergenti, purché abbiano proprietà simili."

Un attacco di soddisfacibilità booleano montato su un circuito camuffato dinamicamente può facilmente produrre una chiave errata e fuorviare l'attaccante. Credito:Rangarajan et al.

Per promuovere l'attuazione della loro tecnica di difesa, i ricercatori prevedono anche un'integrazione basata su spin CMOS ibrida. Questa integrazione potrebbe facilitare l'adozione e l'accettazione del loro schema, nonché dei dispositivi che lo supportano. Secondo i ricercatori, diversi studi accademici si stanno attualmente dirigendo in direzioni simili.

Rangarajan e i suoi colleghi stanno ora pianificando di indagare sulle implicazioni dell'uso del polimorfismo di runtime per proteggere i circuiti logici approssimativi, che negli ultimi anni hanno riscosso molto successo. Questi tipi di circuiti compensano la precisione dell'uscita con una forte riduzione della dissipazione di potenza.

"Soprattutto con l'avvento dell'Internet-of-Things (IoT), riteniamo fondamentale anche la protezione dei chip di calcolo approssimativi, dato che sono ampiamente preferiti per essere utilizzati in sistemi che richiedono un funzionamento a bassa potenza, " ha detto Rangarajan. "Abbiamo anche in programma di valutare la resilienza del nostro schema in altri scenari di attacco, acquisire ulteriore fiducia nel nostro approccio".

© 2018 Science X Network