Credito:Samsung

"Il processo nanometrico si occupa dello spazio tra i transistor montati su un substrato a livello nanometrico, " disse impulso .

"Più stretta è la distanza, più chip possono essere spremuti per aumentare la potenza di calcolo e l'efficienza energetica. Un nanometro corrisponde a un decimillesimo del diametro di un capello umano".

Al Samsung Foundry Forum di Santa Clara, California, l'azienda ha recentemente cercato di impressionare i progressi compiuti nello sviluppo del processo GAA (gate-all-around) a 3 nm.

Samsung Foundry ora introduce MBCFET (FET multi bridge channel). Questo è costituito da nanofogli multi-stack. Con la formazione del nanofoglio, è possibile ottenere una corrente maggiore per stack, disse SamMobile .

ExtremeTech ha descritto l'annuncio come relativo a "un nuovo, un'architettura a transistor evoluta" proveniente da Samsung Foundry, che prevede l'approccio "nanosheets" per il suo nodo a 3 nm.

(Dalla redazione di Samsung:"GAA convenzionale basato su nanofili richiede un numero maggiore di stack a causa della sua larghezza di canale effettiva ridotta. D'altra parte, La versione brevettata di Samsung di GAA, MBCFET (FET multi-ponte-canale), utilizza un'architettura nanosheet, consentendo una maggiore corrente per stack.")

Il blog CNXSoft ha ulteriormente chiarito perché la transizione dai nanofili ai nanofogli.

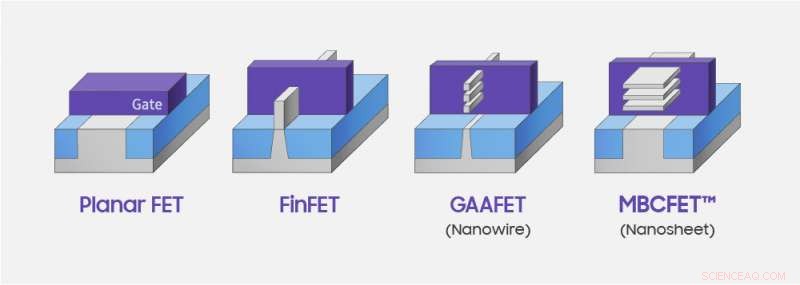

"Spesso leggiamo che i nuovi processori sono prodotti con un processo FinFET. Il nuovo processo è stato creato a causa degli effetti del canale corto nei tradizionali transistor planari, e FinFET (Fin Field-effect transistor) è stato introdotto per consentire un ulteriore ridimensionamento della tensione ma con il nodo di processo che diventa sempre più piccolo, gli effetti elettrostatici hanno iniziato a causare problemi."

L'uso dei nanofili GAA (Gate All Around) per limitare questi effetti è stata considerata una risposta, ma quelli sono apparentemente davvero difficili da integrare nel silicio, ha detto il blog, quindi Samsung ha finito per utilizzare strati sottili (nanofogli) invece di nanofili, "abilitando una maggiore corrente per traccia nella loro implementazione GAA chiamata MBCFET (Multi-Bridge Channel Field-Effect Transistor)."

Per chi ha necessità di elaborare il sovraccarico di sigle, Ramish Zafar in Wccftech ha portato i suoi lettori lungo il viaggio di Samsung. 1. Samsung ha collaborato con IBM per i nodi di processo GAAFET (Gate-All-Around). 2. Ora l'azienda ha annunciato le sue personalizzazioni al processo precedente, e questo è MBCFET.

Zafar ha avuto altro da dire su MBCET. "A differenza dei tradizionali progetti FinFET, GAAFET consente al materiale del cancello di circondare il canale da tutti i lati. Samsung afferma che il design di MBCFET migliorerà il comportamento on-off del processo, e consentire ai processori di ridurre la tensione operativa al di sotto di 0,75 V. Un punto cruciale per MBCFET è che il processo è completamente compatibile con i progetti FinFET e non richiede nuovi strumenti per la produzione".

Credito:Samsung

Come, anche se, tutte queste buone notizie figurano nei piani di sviluppo dell'azienda. Quando possiamo aspettarci di vedere la tecnologia in azione? Joel Hruska ha affrontato questo in ExtremeTech .

"Al suo Samsung Foundry Forum questa settimana, Samsung ha dichiarato che il suo Product Design Kit per chip 3nm è ora in alpha, aver raggiunto il traguardo di sviluppo 0.1. Samsung sta pianificando di lanciare una pletora di nodi di processo nei prossimi anni, con piste di sviluppo previste per 7nm, 6nm, 5nm, 4nm, e sì, 3nm."

Hruska ha aggiunto, "I miglioramenti per 3 nm rispetto a 7 nm sono abbastanza buoni, ma questo nodo non verrà effettivamente spedito per un po' di tempo." Il suo articolo contiene un grafico che mostra la progressione come comunicato da Samsung.

© 2019 Science X Network